Zybo board 开发经验分享第一季: 详解硬件构架

为了学习 RISC-V 以及体验看看 Xilinx 的开发平台,最近我入手了 Zybo Board ,这是一块具有 FPGA 同时又包含了 ARM Cortex-A9 双核心的开发板。

在我们开始这一切之前,我们需要稍微了解一下这片开发板以及他的外围等信息。

要了解 Zybo Board 的外围,首先要看的就是开发商 DIGILENT 所提供的 ZYBO FPGA Board Reference Manual。让我们来看看一些比较重要的地方吧!

基本硬件认识

拿到手的 Zybo Board 会像下面这个样子,我们有这些基本的输入/输出模块,以及未标示的部份(Pmod),可以做延伸的功能

让我们来看看这些外围模块吧

电源输入(5V)

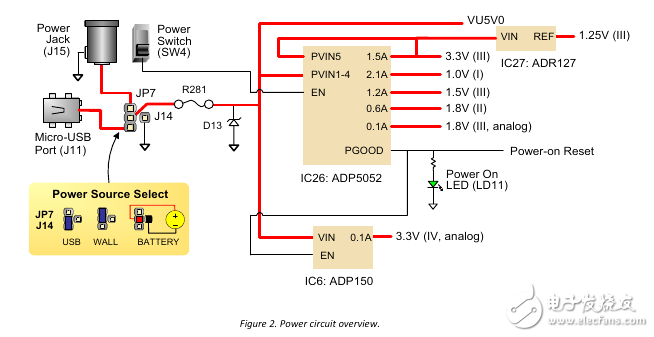

Zybo Board 允许三种不同类型的电源输入模式,分别是 USB、外接电源(J15)、外接电池。我们可以从Reference Manual 得到电源模块的大致信息。

控制电源输入的位置在 JP7 的排针座上,我们可以透过切换跳线(Jumper)来选择我们需要的电源输入,在外围使用不多的情况下,我会直接使用 USB (5V) 来作为电流的输入。

要注意到的是,Zybo Board 仅吃 5V 电源,因此不论你是用外接电源(J15)或是外接电池,你最好都先确认你的电压是否为 5V (或是低于) ,否则你的开发板可能因此烧坏。

插上电源后,透过电源开关 (Power Switch, SW4) 的切换即可完成给电/断电的动作。

Zynq SOC

Zybo Board 核心是 Xilinx Zynq-7000 系列的 Z-7010 ARM/FPGA SoC 处理器,这是一种混和了 FPGA 以及 ARM Cortex-A9 处理器的 FPGA 核心。以往的 FPGA 开发板需要用到 CPU 的时候只能够刻录用 HDL 语言撰写的软核心到开发板上,这种混搭 FPGA/ARM 的开发板则是让你可以针对通用需求使用 ARM CPU 进行程序的开发,特殊需求则透过 FPGA 进行处理/加速来运作,是一种蛮有趣的架构。

我们可以把 Zynq SoC 分为两个区块, 处理系统 (Processing System, PS) 以及 可程序逻辑区块(Programmable Logic, PL),像这样处理系统(Processing Syste, PS) 也就是有 ARM Cortex-A9 处理器的部份,可程序逻辑区块(Programmable Logic, PL) 则是 FPGA 所包含的部份。

在上面的区块图中,我们要另外注意到 MIO (MulTIplexed I/O) 以及 EMIO (Extended mulTIplexed I/O),在 Zynq 7000 系列 SoC 中,我们共有 54 个 MIO 可用,而这些 MIO 所连接的地址是无法在 可程序逻辑区块 (Programmable Logic, PL) 中看到。

在 Zybo Board 我们有这几个地方是连接到 MIO (MulTIplexed I/O) 上的

系统启动流程

由于 Zynq 7000 系列内建了 ARM CPU,也因此和传统的 FPGA 开发板相比,系统启动流程也会不同,整体开机流程可以分为三个阶段:

o 阶段 0

当 Zybo board 电源启动后,CPU0 会执行内部已经预刻录的程序 BootROM,这个程序会根据 JP5 所设定的信息来更新状态缓存器(mode register),接着 BootROM 会透过状态赞存器(mode register)的信息从 MicroSD、NOR Flash、JTAG 等位置抓取 Zynq Boot Image,并将包在 Zynq Boot Image 里面的 第一级启动开机程序 (First Stage Bootloader, FSBL) 复制到内部 256KB 的内存 (On-Chip Memory, OCM) 去,最后执行 FSBL,进入下一个阶段。

如果 BootROM 是因为按下了 RESET 按钮等状况而被执行,Zybo board 会选用之前已经存放在状态缓存器(mode register)的开机状态,而不是当下的 JP5 状态。

o 阶段 1

在这阶段中, 第一级启动开机程序 (First Stage Bootloader, FSBL) 初始化了 DDR 内存、GPIO 等外围设定,接下来会加载存放在 Boot Image 内的比特流 (bitstream),用他来对可程序逻辑区块 (Programmable Logic, PL) 进行设定。

当可程序逻辑区块(Programmable Logic, PL)设定完成后,FSBL 会去加载程序(ex: u-boot)并执行它。

o 阶段 2

最后的接段即是执行 FSBL 所加载的程序,这些程序可以从简单的 "Hello World",到像 u-boot 这样的第二阶段开机程序,用来加载 Linux 或是其他的操作系统。

更改开机模式

我们可以透过切换 JP5 的跳线(Jumper)来决定我们要透过哪种方式去加载第一级启动开机程序 (First Stage Bootloader, FSBL)

MicroSD 启动

当使用者将 MicroSD 插入到 J4 的 SD 卡槽,并设定好 JP5 的跳线的话,我们可以透过 MicroSD 来进行开机的动作。

若你希望透过 MicroSD 进行开机,你需要先设定好你的 SD 卡:

1. 透过计算机格式化 MicroSD 卡成 FAT32 文件格式

2. 复制从 Xilinx SDK 制作出来的 Zynq Boot Image 到 MicroSD 卡上

3. 将 Zynq Boot Image 命名为 BOOT.bin

4. 将 MicroSD 卡从计算机移除,并插入到 Zybo Board 的 J4 SD 卡槽上

5. 接上电源,并设定好 JP7 (Power Source Select)

6. 将 JP5 的跳线 (Jumper) 调整到 MicroSD 模式 (板上标示为 SD 的那个)

7. 启动电源。接下来 Zybo Board 就会从 MicroSD 卡启动。

- Zybo全栈开发入门教程(基于Linux嵌入式系统):10个步骤自定义IP模块(02-07)

- 编译环境和交叉编译环境的搭建(02-08)

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)