Zybo board 开发经验分享第一季: 详解硬件构架

QSPI 启动

在 Zybo board 上有一颗 128-Mbit Quad-SPI (QSPI) 的 NOR Flash,我们可以透过 Xilinx ISE 和 Vivado 等工具去将 Zynq Boot Image 下载到 QSPI Flash 上。

当下载完成后,照这样的步骤即可透过 QSPI 启动:

1. 接上电源,并设定好 JP7 (Power Source Select)

2. 将 JP5 的跳线 (Jumper) 调整到 QSPI 模式 (板上标示为 QSPI 的那个)

3. 启动电源。接下来 Zybo Board 就会从 QSPI 卡启动。

JTAG 启动

当你将 JP5 设定为 JTAG 启动模式,Zynq 内的 Cortex-A9 处理器会等到计算机端的 Xilinx 工具加载了要执行的程序之后,再执行预执行的程序,或是启用一步一步(step-by-step)的执行模式来方便我们除错。

除此之外,我们也可以透过 iMPACT 或是 Vivado Hardware Server 透过 JTAG 来设定可程序逻辑区块 (Programmable Logic, PL)。

Zybo Board 默认是开机启动 Cascaded JTAG 模式,在这种模式下 处理器系统 (Processing System, PS) 和 可程序逻辑区块 (Programmable Logic, PL) 可以透过同一个 JTAG 去进行控制。如果你将 JP6 短路,则可以让 JTAG 仅看得到 可程序逻辑区块 (Programmable Logic, PL),在这种状况下,使用者可以透过 EMIO (Extended mulTIplexed I/O) 将 PJTAG 拉出,让外部的设备可以和 处理器系统 (Processing System, PS) 进行沟通。

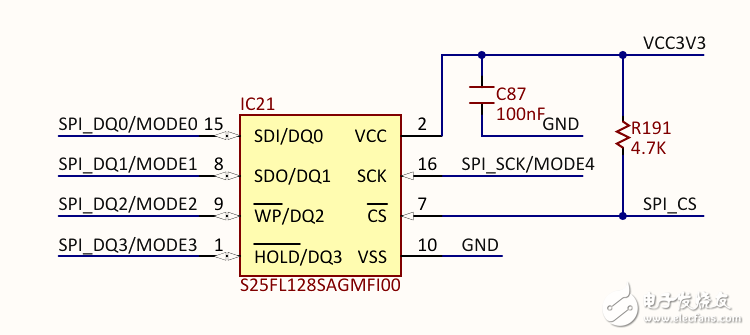

SPI Flash

Zybo Board 内建了 4-bit SPI (QSPI) NOR Flash,硬件型号为 Spansion S25FL128S。

假设 JP5 设定为 NOR Flash 开机,则我们可以透过这颗 NOR Flash 来初始化处理器系统(Processing System, PS)以及可程序逻辑区块(Programmable Logic, PL)。除此之外,当开机完成后,我们可以使用 Spansion 文件系统(Spansion Flash File System, FFS) 来对档案进行读写的处理。

从电路图我们可以看到 SPI Flash 是直接连到 Zynq 处理器上的 Quad-I/O SPI interface。

DDR 内存

Zybo Board 使用的是 Micron MT41J128M16JT-125 或是 MT41K128M16JT-125 这两种 DDR3 内存组件,在 Zybo Board 上我们共有 512MB 的内存空间可以使用。

根据 Zynq-7000 All Programmable SoC Technical Reference Manual,DDR3 内存是直接连接到处理器系统 (Processing System, PS)。

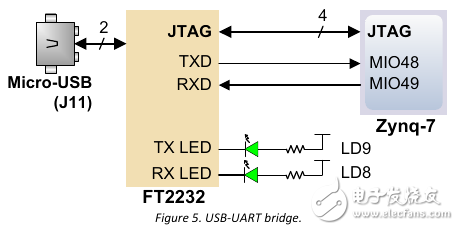

USB UART 接口

Zybo Board 并未将 UART 串行端口拉出,取而代之的它采用了 FTDI FT2232HQ 这款 USB 转 UART 的 IC 让你的计算机可以和 Zybo Board 进行沟通。

如果你是 Linux 使用者,在安装完 Vivado 后,你会需要手动安装 udev 设定好让 Linux 可以侦测到这个 USB 转 UART 设备(共两组,/dev/ttyUSB0, /dev/ttyUSB1),假设你的 vivado 安装在 /opt/Xilinx/Vivado/2016.1的话,我们可以透过以下程序来安装 udev 设定。

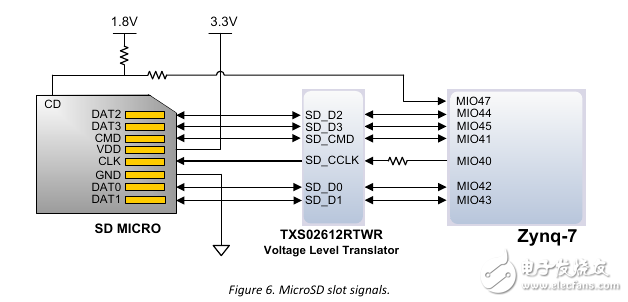

MicroSD 插槽

在 Zybo Board 的背面,我们可以看到 Micro SD 插槽(J4),根据 Zynq-7000 All Programmable SoC Technical Reference Manual ,Zynq 的 SDIO 控制器仅支持 1-bit 或是 4-bit 传输模式 (Host Modes),不支持 SPI 模式。

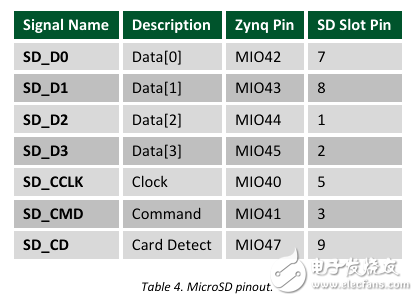

而 Micro SD 使用到的 MIO (Multiplexed I/O) 信息如下:

USB OTG

Zybo Board 提供了一组 USB OTG 支持,在这个界面中使用了 Microchip 的 USB3320 这颗 IC 来作为端口物理层 (Port Physical Layer, PHY),要注意到的是,你不可以 同时 将 USB 主机 (HOST) 以及 USB 设备 (Device) 接到 USB OTG 端口上。

(也就是不要同时接上设备到 J9 以及 J10)

而在 USB OTG 的功能上,我们则是用掉了 MIO 28 ~ 39 的位置。

另外,由于 USB 2.0 的规格是 USB 主机最多可以提供 500mA 的电流,当你设定为 USB 主机的模式时,在 J11的电源端 必须 改用外接电源或是电池输入,避免电流不够的情况发生。

Ethernet PHY

Zybo Board 使用 Realtek RTL8211E-VL PHY 来实现 10/100/1000 网络传输的功能。具体使用到的 MIO 以及 EMIO 接脚信息如下:

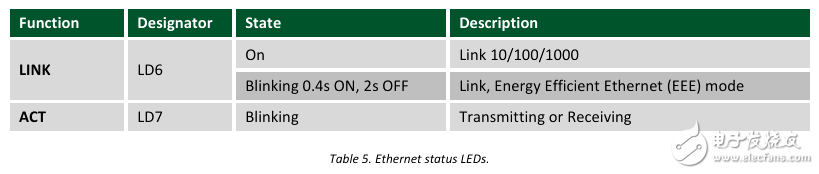

我们可以透过在 RJ45 附近的 LED 来观察流量 (LD7) 以及联机状态 (LD6) 的信息

网卡的 MAC 地址则是存放在 Micrichip 24AA02E48 这颗 EEPROM 上面,Zynq 处理器透过 EMIO 上的 I?C 接口来和 EEPROM 进行沟通。

HDMI Source/Sink

Zybo Board 的 HDMI 接口并未透过外部 IC 去驱动,因此我们必须透过可程序逻辑(Programmable Logic, PL) 去实现影片编码 (Encoding)与译码(Decoding)的功能。

由于 Zybo Board 的 HDMI 接口支持 HDMI 来源装置(HDMI Source) 以及 HDMI 目

- Zybo全栈开发入门教程(基于Linux嵌入式系统):10个步骤自定义IP模块(02-07)

- 编译环境和交叉编译环境的搭建(02-08)

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)