Zybo全栈开发入门教程(基于Linux嵌入式系统):10个步骤自定义IP模块

Zybo是Digilent公司推出的一款基于Xilinx Zynq-7000系列中最小型号Z7010 SoC的嵌入式开发平台,zybo上集成了丰富的多媒体外设接口,强大的Z7010芯片支持完成的系统设计,同时五个Pmod接口提供了丰富的扩展空间,想必很多人都听说过zedboard的大名,其实可以说zybo是mini-zedboard。Zybo全栈开发教程共分为三部分:自定义IP、移植Linux操作系统、编写驱动模块和应用。通过这三部分你将能够全面熟悉Zynq AP SoC架构的开发流程,包括FPGA逻辑电路设计、软件编程、Linux操作系统及软件开发,以及如何在Zybo开发板中应用这些技能。

在这个教程中,我们将以Digilent官网提供的Zybo Base System Design作为基础。它的架构如图。可以看到,UART1连接到USB-UART, SD0连接到SD Card Slot, USB0连接到USB-OTG port, Enet0连接到Giga-bit Ethernet Port,GPIO连接到Btn4/5,以及Quad SPI连接到on-board QSPI Flash。这些处理系统(Processing System, 简称PS)内的硬件IP通过复用I/O接口连接到板上的外设。在可编程逻辑(Programmable Logic, 简称PL)的部分,我们有HDMI Tx Controller, VDMA, I2C以及GPIO等等IP核。更多的资料可以看下载这个Zybo基本系统时包含的文件。

教程开始之前我们要先明确所需要的资料如下:

Zybo Board硬件板卡

Vivado 2014.1 Webpack软件开发环境

Zybo Base System:板卡底层基础配置

U-boot:与ZYBO板卡硬件设计相关

Linux内核源码

根文件系统

注:相关资料可以在Digilent的GitHub账户上找到(即 https://github.com/DigilenTInc )

自定义IP就是让用户在Zynq SoC的FPGA部分实现自己的功能模块逻辑设计:

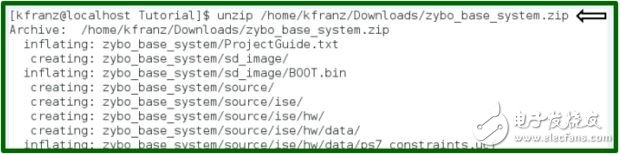

步骤一:下载zybo base system文件

根据自己的设计下载zybo base system压缩包文件并解压到指定目录

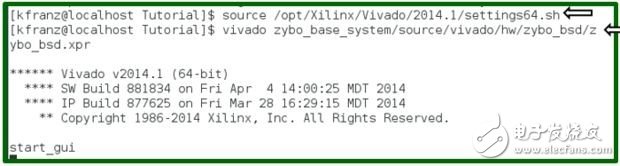

步骤二:使用vivado工具打开zybo base system文件

首先我们需要设置Vivado的环境变量,共有四个选项分别是setTIngs64.sh、setTIngs32.sh、setTIngs32.csh和settings64.csh,请根据机器系统是32位还是64位以及bash版本来使用。

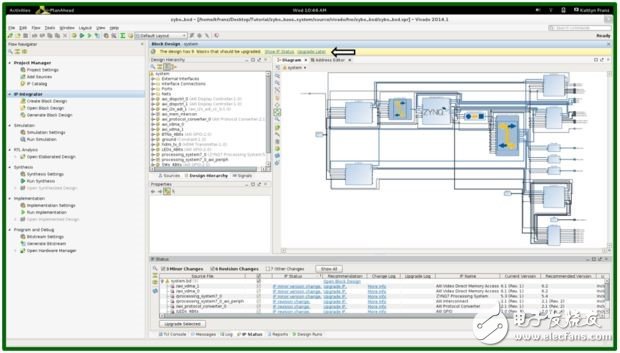

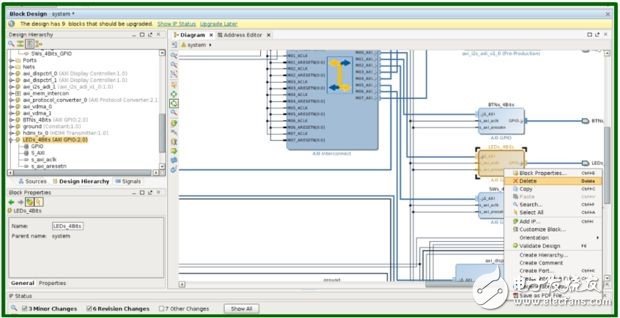

步骤三:删除已存在的LED模块

首先我们要确保所有的IP模块状态保持最新状态,如果有更新就会在顶部显示一条黄色的提示栏,点击更新(upgrade)即可,然后在base system中已经预先设置了一个LED模块,这个模块主要采用PS的I/O接口,我们要把这个IP删除(如第二张图所示)。

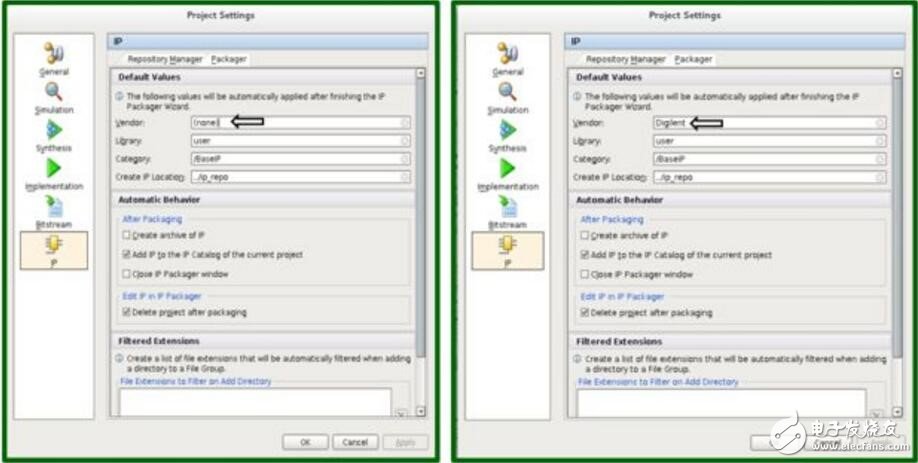

步骤四:设置ip核Vendor

在创建myLed IP核之前我们要Project Settings里面设置Vendor选项的名字,否则会引起Vivado软件内部异常,名字可以根据自己喜好随意设置。

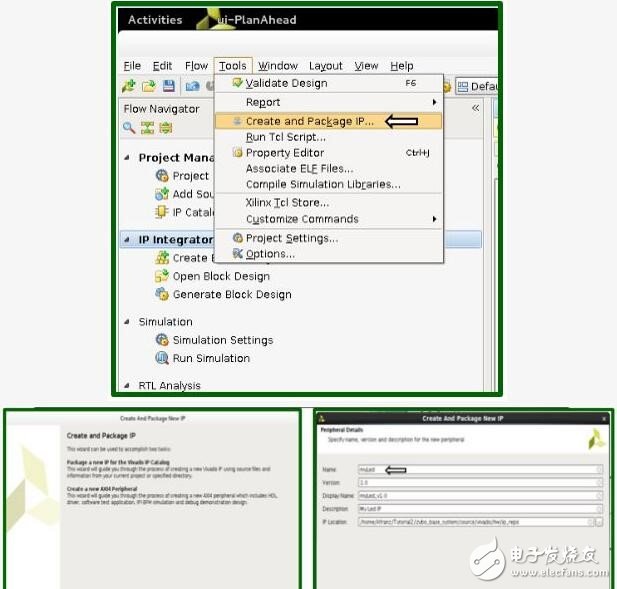

步骤五:创建myLed IP模块

点击菜单栏Tools—>Create and Package IP,弹出的对话框选择Create a new AXI4 Peripheral,然后在弹出的对话框输入IP名字、版本、存储位置等相关信息,点击Next继续下一步。

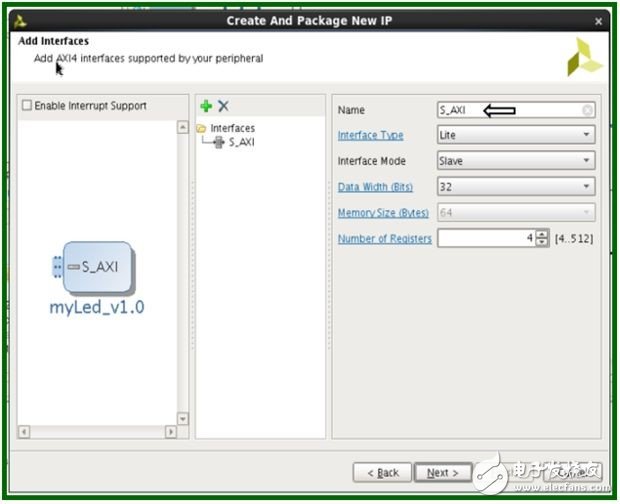

步骤六:增加模块接口

myLed IP采用AXI4外设接口,接口类型为Lite,模式为Slave,数据宽度32bits,寄存器数量为4,确保Name选项为S_AXI,实际上我们只需要一个寄存器,但是最小设置为4。

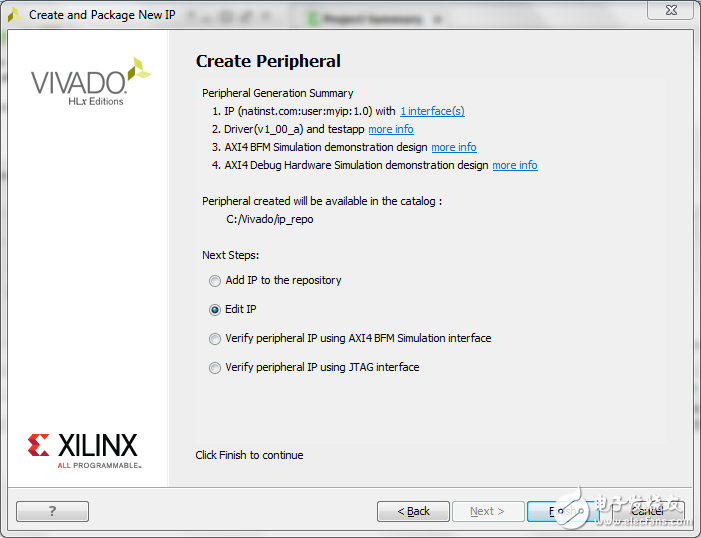

步骤七:编辑IP功能逻辑代码

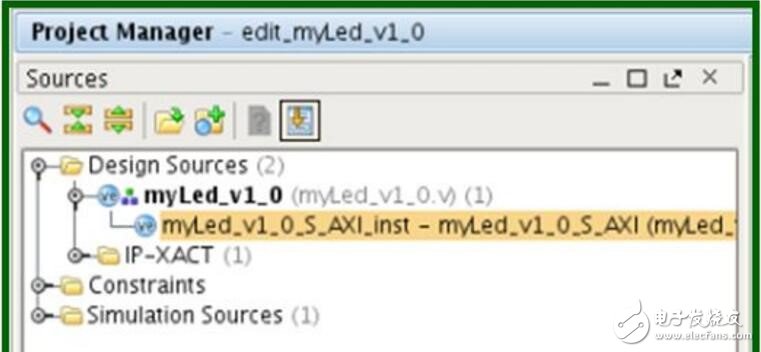

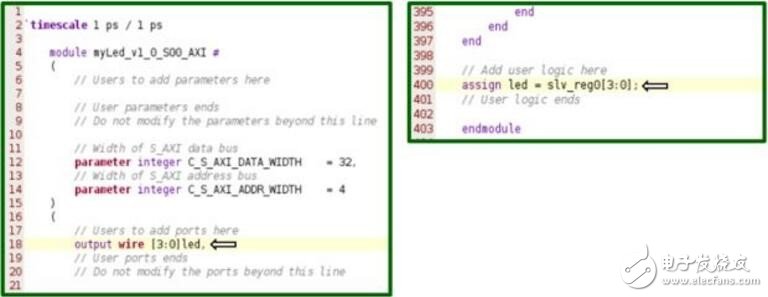

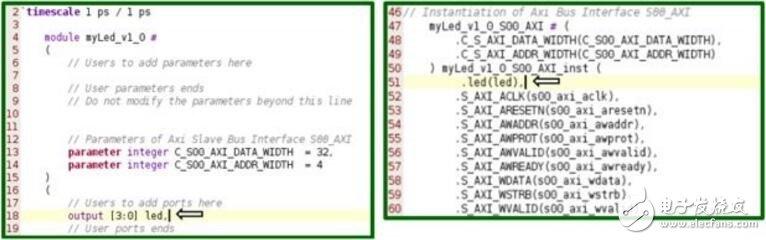

基本设置完成后点击Next,我们需要选择Edit IP,然后添加用户定义的逻辑。我们要修改两个文件,分别是MyLed_v1_0_S_AXI和MyLed_v_0(对应上图顺序),经过上面的修改我们将slv_reg0[3:0]与输入端口led[3:0]连接起来。

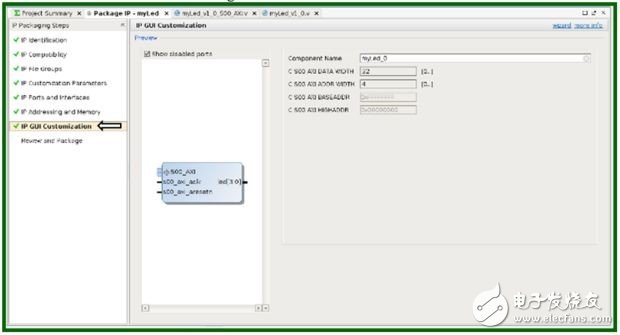

步骤八:封装IP模块

通过步骤七我们定义了IP逻辑,然后我们需要将它打包为一个黑盒,在Project Manager下拉菜单选择Package IP,根据提示进行设置,保证弹出的对话框右侧选项全部打上绿勾。

步骤九:将自定义IP myLed_v1.0增加到系统中

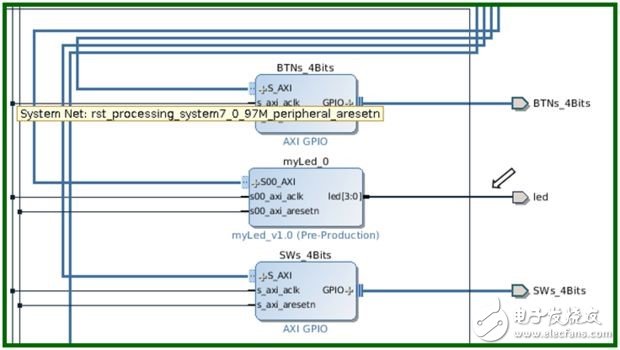

在block design的空白处右键选择add IP,搜索myled找到刚才封装的IP。增加myLed_v1.0模块后,对话框顶部会出现绿色的提示框,我们点击Run connection Automation,这个操作会将myLed IP的AXI4-Lite总线与PS连接起来。

步骤十:连接外部led端口

在空白处点击右键选择Create Port,设置为output,位宽led[3:0],然后用鼠标拖拽将这个输出端口与myLed_0的输出接口led[3:0]建立连接。

步骤十一:修改约束文件,生成比特流文件

打开Constraints下拉菜单下的base.xdc管脚约束文件,将led[3:0]与FPGA硬件管脚绑定,即与zybo板上的四个led灯连接,最后在Program and Debug下拉菜单中选择Generate Bitstream,至此自定义用户IP并生成比特流文件完成。

下篇文章中将向大家介绍在本篇内容基

- Zybo board 开发经验分享第一季: 详解硬件构架(02-07)

- 编译环境和交叉编译环境的搭建(02-08)

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)