cmos+忆阻器实现高效分布式处理兼存储功能的传感器架构

曲线。在图c中,非对称输入施加电压(红色)和相应电流(绿色)是时间的函数。图d是非对称输入电流-电压特性曲线。图a中的施加电压是±v0 sin(w0t),而图c中的施加电压是±v0 sin2(w0t), 其中w0 = 2?f0 = 2?u2/D2。

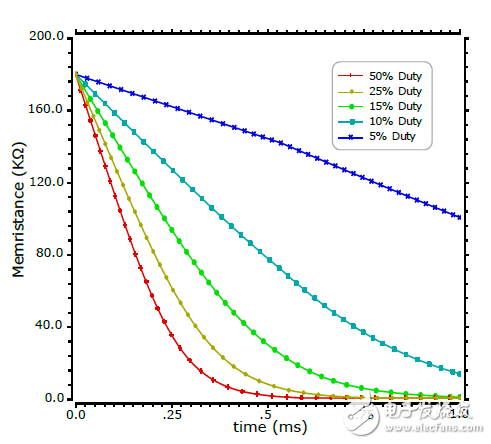

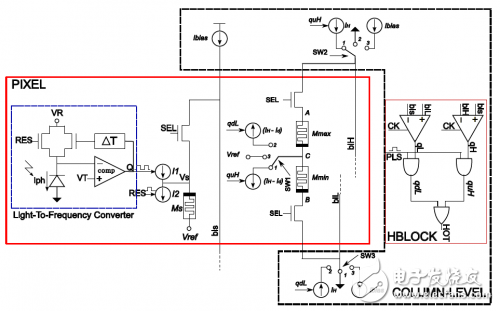

忆阻器初始电阻通常很大,施加极性相反的连续或脉冲电压可使电阻线性降至一个低电阻的谷底,如图3所示。施加极性相反的电压可使忆阻器恢复初始高电阻,恢复时间通常比直接恢复方法短很多。在图3中,忆阻器的初始电阻值很高,向忆阻器施加一序列占空比可控的脉冲频率wp=5w0、电流幅度ip = 160uA的电流脉冲,以此可以向忆阻器写入数据。占空比越高,流经忆阻器的电荷量就越大,导电速度也就越快。忆阻器具有脉冲式非线性编程功能,用光频率转换器作为编程信号源,用与光强成正比的电流脉冲驱动忆阻器,可实现光阻(L2R)编码。如图6的像素架构示意图所示。除其独特的非线性编程外,忆阻器还可视为兼有电容器的存储效应与电阻器的无漏电性。所有这些,结合其小尺度和易实现性,使其成为一个最有趣的模拟信号处理应用元器件,不过,本文只讨论如何在紧凑的像素内使用忆阻器执行背景提取功能。

图3:在使用一系列不同占空比的编程频率wp=5w0、电流幅度ip = 160uA的电流脉冲给阻器编程时的忆阻-时间变化速度

III. 工作原理

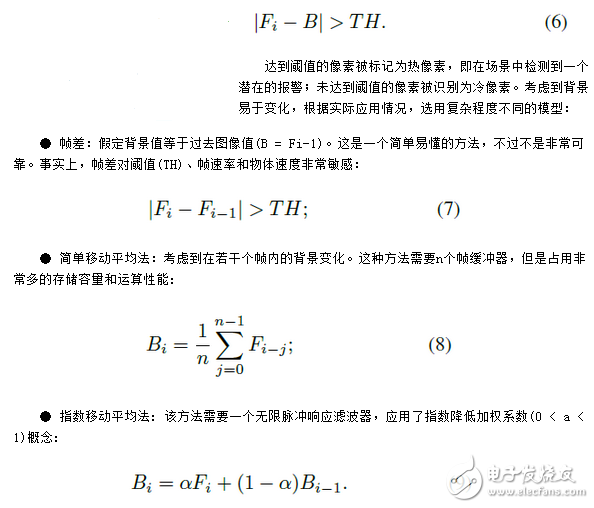

在讨论传感器架构之前,需要描述一下像素级自适应背景提取算法。我们考虑成像传感器的一个像素给一个特定场景点编码的情况。该像素以帧速率fps采集光强,并将其转换成电压VS(nT),其中T = 1/fps是像素传感器采样时间,整数n 表示帧个数。在传感器工作过程中,像素采集的光强呈动态变化,变化速率取决于场景内运动类型或环境光的变化。通过监视信号动态变化和振幅,每个像素需要检查场景中是否发生潜在异常。为此,必须从现有图像(Fi)提取背景(B),然后比较最终差值与正确的阈值(TH):

该方法的主要优点是,不需要增加存储器,通过改变学习速率值a,即可微调滤波器。

考虑到上述方法的硬件实现问题和稳健性,我们利用指数移动平均法和两个电压阈值而非参考文献(6)的一个阈压建立了一个背景模型。阈压定义了信号可以安全变化(冷像素)的电压范围,超过这个安全范围(高于最高阈压或低于最低阈压),信号被视为异常(热像素),可能会触发一次报警。

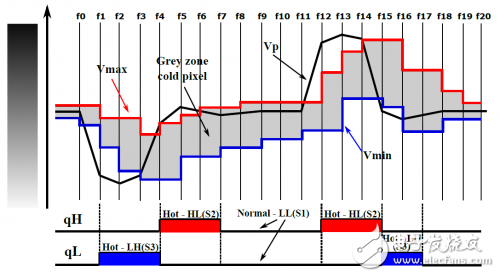

图4:在像素级执行背景动态提取算法

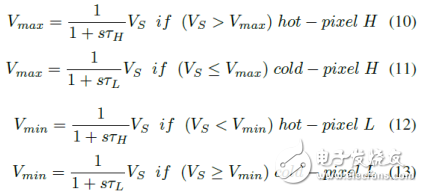

图4所示是背景提取算法的工作原理。该示例是一个单像素在20帧期间的工作情况。黑色曲线表示像素获取的信号电压VS,红线(Vmax)和蓝线(Vmin)波形是界定灰色区上下边界的两个阈压值的集合,在灰色区域内,信号可以自由变化,不会出现任何报警。信号电压VS经低通滤波后生成信号,每个滤波器在两个时间常量(tH < tL)之间开关操作,具体情况取决于下面条件:

其中,等式(10)和(12)分别表示Vmax和Vmin的热像素条件,而等式(11)和(13)则表示冷像素条件。两个阈值的行为界定了一个根据信号动态在一段时间内变化的灰色区域,灰色区域代表VS未发现异常条件的运动的电压范围,例如,如果VS突然从亮变暗,越过灰色区域上边界(Vmax),则生成一个热像素。

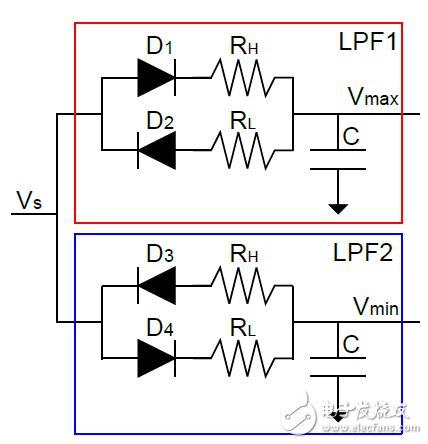

图5:两个一阶低通滤波器生成图4中的两个阈压。

因此,当Vmax试图快速触达VS过程中,Vmin也在做同样的事情,只不过速度较慢。这里,灰色区域快速变大。在若干个帧后,两个阈压限制VS,吸收全部信号变化,这样不会再产生任何热像素。从此,灰色区域恢复窄状和最大像素敏感度。

图6:利用内部三个忆阻器执行动态背景提取的像素示意图

IV. 像素实现

可以用两个理想的低通滤波器来实现等式(10)-(13)。如图5所示,LPF1实现等式(10)和(11),LPF2实现等式(12)和(13)。假设理想二极管D1-D4(无电压降),且RL > RH, 每个模块实现两个不同的一阶阻容滤波器,TH = RHC,且TL = RLC, 其中RH >> RL。监视场景中的事件需要从几秒到几十秒的大范围时间常数滤波器,这意味R和C应该分别是兆欧和微法量级的电阻器和电容器。每个模块(LPF1, LPF2)都必须能够从一个时间常数切换到另一个时间常数,从而取得自适应算法所需的行为特性。为取得一个高效的视觉传感器架构,这种双边峰值检测和滤波操作必须在像素附近的位置完成。为此,有些人提出定制cmos传感器解决方案,使用开关电容器技术模拟每个像素里面的两个滤波器。不过,这种设计方法有以下两个缺点:(a) 两个阈压值在模拟存储器内的保留时间达不到应用的求;(b)充当模拟存储单元的电容器占用的芯

- 非一般的晶体管(10-12)

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)

- 一种低压高线性CMOS模拟乘法器设计(04-01)

- 基于0.25 μm N阱CMOS工艺下的CMOS带隙基准电压源设计方案(03-14)

- CMOS电路IDDQ测试电路设计(04-24)

- 一种新型的高性能CMOS电流比较器电路(03-05)