一种低压高线性CMOS模拟乘法器设计

四象限模拟乘法器是模拟信号处理系统中的重要组成单元,它被广泛地应用于锁相环、频率变换、调制与解调、自适应滤波等许多模拟信号处理电路中。目前,适应于低压工作的CMOS四象限模拟乘法器由6个级联的两输入组合结构单元(Combiner)组成,这种结构已广泛应用于射频电路中,它的NMOS管分别对源漏相接,且通过负载电阻R直接到电源。因它的输入电压可直接控制晶体管电流,因而该乘法器工作所需要的电源电压很小,其最小的电源电压是NMOS栅源电压与负载电阻上的压降之和。但是这种乘法器结构含有较多的电流支路,电阻也相对较多,一定程度上增加了版图的面积和功耗,最重要的是该结构对MOS管的匹配有严格要求,否则线性度很难保证,这样也就对制造工艺提出了较高的要求。针对这一缺点,本文提出了一种新型模拟乘法器结构,它采用减法电路来提高电路的线性度。

1 电路工作原理

1.1 设计思路

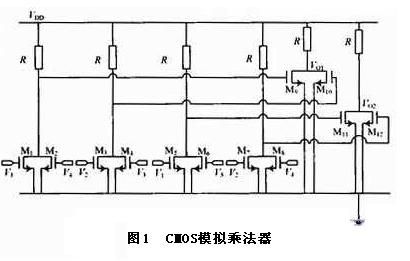

图1给出适应于低压工作的CMOS四象限模拟乘法器结构(Cornbiner)。它的输出电压为:

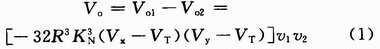

输出电压:

式中:V1=Vx+v1;V2=Vx-v1;V3=Vy+v2;V4=Vy-v2;Vx,Vy是共模电平,v1,v2是差模电平;KN是晶体管的跨导参数;VTN是NMOS的阈值电压。

本文提出的新型模拟乘法器结构基于MOS管工作在饱和区的平方律特性实现了乘法运算,不仅省去图1所示乘法器电路中的多个电阻,也减少了电路的面积和功耗,最重要的是降低了晶体管对匹配的严格要求,因此可以提高电路的线性度。

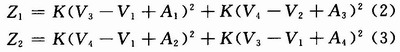

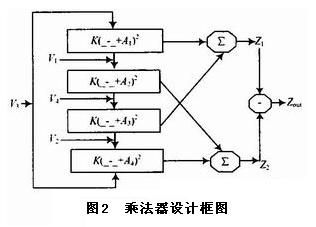

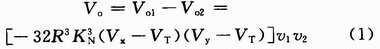

图2所示为该乘法器电路的设计框图。由图可知,

不管A1,A2,A3,A4是常数或者与输入信号有关,假设A1=A2=A3=A4,Vidl=V1-V2,Vid2=V3-V4,最后的差分输出:

这样最终就实现了乘法运算功能。

1.2 电路实现

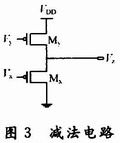

式(2)与式(3)中的平方运算可以由4个工作在饱和区的NMOS管实现,平方项中的减法运算可以由减法电路实现,如图3所示。

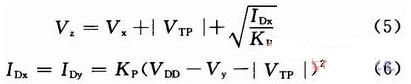

由图3可知,Vz与Vx之差就是Mx管的栅源电压,而且Mx管的栅源电压大小与输入电压Vy有关。假设Mx管与My管参数一样,有:

这里VTP是PMOS的阈值电压。由式(2)与式(3)相减,得:

将这种减法电路和4个工作在饱和区的NMOS管相结合,得到一种新型的CMOS四象限模拟乘法器,如图4所示。

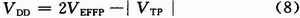

如上述,定义图4中2个差分输入对分别为Via1=V1-V2;Vid2=V3-V4,输出端Vo1,Vo2。为了使电路工作在饱和区,最小的电源电压必须满足:

式中:VEFFP为PMOS管的饱和压降。

对于深亚微米级CMOS工艺,一般PMOS管的阈值电压绝对值可低至0.6 V以下,因此只要合适选择晶体管尺寸,电路工作的电源电压可低至1 V。

利用式(7),输出端Vo1,Vo2的输出电压:

最终输出Vo,由式(6)、式(7)相减可得:

由输出式(11)可知,该乘法器的输出增益仅由负载电阻R,以及M9~M12晶体管的跨导参数决定。相比图1所示电路结构,节约4个电阻,减少了版图面积,电路结构更为简单。

四象限模拟乘法器是模拟信号处理系统中的重要组成单元,它被广泛地应用于锁相环、频率变换、调制与解调、自适应滤波等许多模拟信号处理电路中。目前,适应于低压工作的CMOS四象限模拟乘法器由6个级联的两输入组合结构单元(Combiner)组成,这种结构已广泛应用于射频电路中,它的NMOS管分别对源漏相接,且通过负载电阻R直接到电源。因它的输入电压可直接控制晶体管电流,因而该乘法器工作所需要的电源电压很小,其最小的电源电压是NMOS栅源电压与负载电阻上的压降之和。但是这种乘法器结构含有较多的电流支路,电阻也相对较多,一定程度上增加了版图的面积和功耗,最重要的是该结构对MOS管的匹配有严格要求,否则线性度很难保证,这样也就对制造工艺提出了较高的要求。针对这一缺点,本文提出了一种新型模拟乘法器结构,它采用减法电路来提高电路的线性度。

1 电路工作原理

1.1 设计思路

图1给出适应于低压工作的CMOS四象限模拟乘法器结构(Cornbiner)。它的输出电压为:

输出电压:

式中:V1=Vx+v1;V2=Vx-v1;V3=Vy+v2;V4=Vy-v2;Vx,Vy是共模电平,v1,v2是差模电平;KN是晶体管的跨导参数;VTN是NMOS的阈值电压。

- 获取较高的低压输出精度小技巧(10-11)

- 一种应用于开关电源的低压高增益三级放大比较器(07-21)

- 低压单阈值开关电荷泵实现方案(12-09)

- 旧开关电源代换电磁炉低压电源的设计方案(02-16)

- 无功补偿技术对低压电网功率因数的影响 (05-02)

- 低压差(LDO)调节器的噪声源(03-09)