采用自举升压结构设计双电压mosfet驱动电路

此在实际设计时,Cboot的取值要大于式(5)的计算结果,这样可以提高B点电压,降低N4导通电阻,减小驱动电路的上升时间。

P2、P4的尺寸问题

将公式(5)重新整理后得:

V_{B}=({V_{DD}-V_{thn})\frac{C_{boot}}{Cpar}-V_{thn}\frac{C_{A}}{Cpar} (6)

从式(6)中可以看出在自举升压周期内,A、B两点的寄生电容使得B点电位降低。在实际设计时为了得到合适的B点电位,除了增加Cboot大小外,要尽量减小A、B两点的寄生电容。在设计时,预充电PMOS管P2的尺寸尽可能的取小,以减小寄生电容CA。而对于B点的寄生电容Cpar来说,主要是上拉驱动管N4的栅极寄生电容,MOS管P4、N3的源漏极寄生电容只占一小部分。我们在前面的分析中忽略了P4的源漏电压,因此设计时就要尽量的加大P4的宽长比,使其在自举升压周期内的源漏电压很小可以忽略。但是P4的尺寸以不能太大,要保证P4的源极寄生电容远远小于上拉驱动管N4的栅极寄生电容。

阱电位问题

如图3所示,PMOS器件P2、P3、P4的N-well连接到了自举升压节点A上。这样做的目的是,在自举升压周期内,防止他们的源/漏--阱结导通。而且这还可以防止在源/漏--阱正偏时产生由寄生SRC引起的闩锁现象。

上拉驱动管N4的阱偏置电位要接到它的源极,最好不要直接接地。这样做的目的是消除衬底偏置效应对N4的影响。

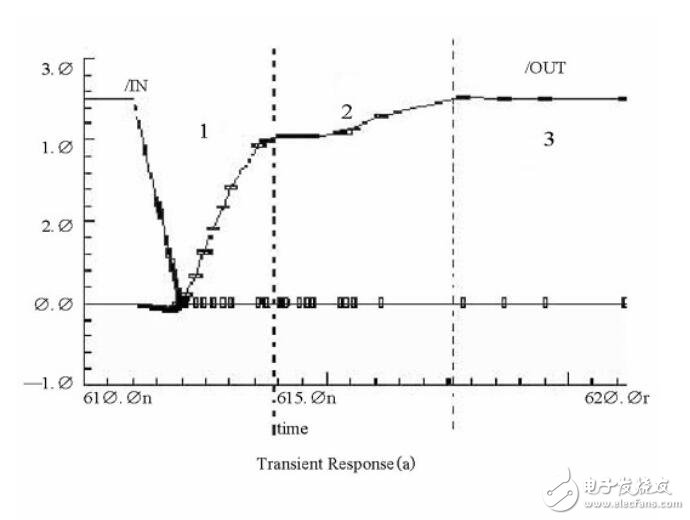

Hspice仿真验证结果

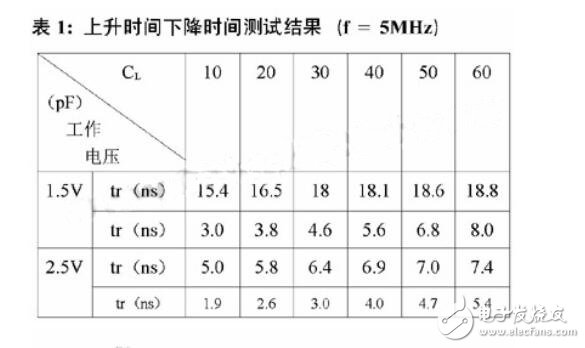

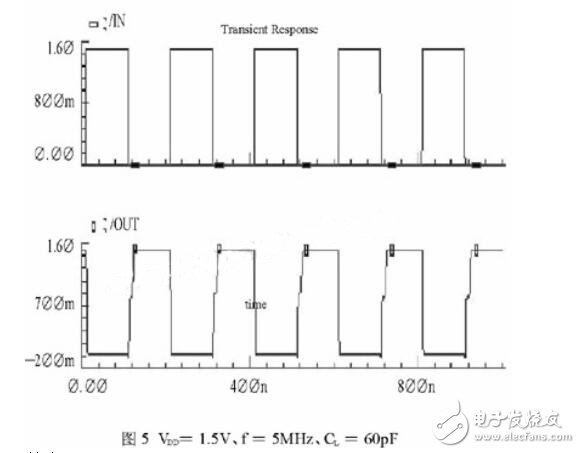

驱动电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证。在表1中给出了电路在不同工作电压、不同负载条件下的上升时间tr和下降时间tf 的仿真结果。在图5中给了电路工作在输入电压1.5V、工作频率为5MHz、负载电容60pF条件下的输出波形。

结合表1和图5可以看出,此驱动电路能够在工作电压为1.5V,工作频率为5MHz,并且负载电容高达60pF的条件下正常工作。它可以应用于低电压、高工作频率的DC-DC转换器中作为开关管的驱动电路。

结论 本文采用自举升压电路,设计了一种BiCMOS Totem结构的驱动电路。该电路基于Samsung AHP615 BiCMOS工 艺设计,可在1.5V电压供电条件下正常工作,而且在负载电容为60pF的条件下,工作频率可达5MHz以上。

- 电容降压LED驱动电路(06-24)

- 新型大功率蓝光LED光源驱动电路设计(08-03)

- 电动自行车控制器MOSFET驱动电路的设计(11-18)

- 两种常见的MOSFET驱动电路设计(12-02)

- 大功率LED恒流驱动电路的设计实例(06-06)

- 高频逆变电源的保护与驱动电路的设计(06-26)