采用自举升压结构设计双电压mosfet驱动电路

MOS管最显著的特性是开关特性好,所以被广泛应用在需要电子开关的电路中,常见的如开关电源和马达驱动,也有照明调光。

现在的MOS驱动,有几个特别的需求,

1,低压应用 当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有0.7V左右的压降,导致实际最终加在gate上的电压只有4.3V。这时候,我们选用标称gate电压4.5V的MOS管就存在一定的风险。 同样的问题也发生在使用3V或者其他低压电源的场合。

2,宽电压应用 输入电压并不是一个固定值,它会随着时间或者其他因素而变动。这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的。

为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值。在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗。

同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗。

3,双电压应用

在一些控制电路中,逻辑部分使用典型的5V或者3.3V数字电压,而功率部分使用12V甚至更高的电压。两个电压采用共地方式连接。

这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题。

在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构。

于是我设计了一个相对通用的电路来满足这三种需求。

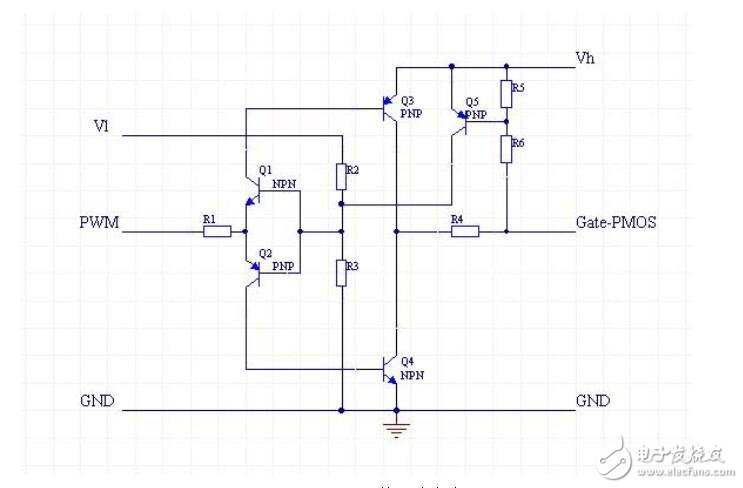

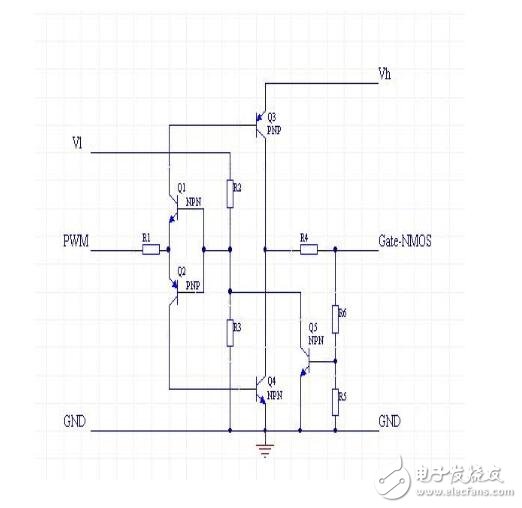

电路图如下:

图1 用于NMOS的驱动电路

图2 用于PMOS的驱动电路

这里我只针对NMOS驱动电路做一个简单分析:Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。 R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。 Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通 常只有0.3V左右,大大低于0.7V的Vce。 R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈, 从而把gate电压限制在一个有限的数值。这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限 制。必要的时候可以在R4上面并联加速电容。

这个电路提供了如下的特性:

1,用低端电压和PWM驱动高端MOS管。

2,用小幅度的PWM信号驱动高gate电压需求的MOS管。

3,gate电压的峰值限制

4,输入和输出的电流限制

5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM信号反相。NMOS并不需要这个特性,可以通过前置一个反相器来解决。

在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题。DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电。目前DC-DC转换器设计技术发展主要趋势有:(1)高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善。小功率DC-DC转换器的开关频率将上升到兆赫级。(2)低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求,这些技术的发展对电源芯片电路的设计提出了更高的要求。

首先,随着开关频率的不断提高,对于开关元件的性能提出了很高的要求,同时必须具有相应的开关元件驱动电路以保证开关元件在高达兆赫级的开关频率下正常工作。其次,对于电池供电的便携式电子设备来说,电路的工作电压低(以锂电池为例,工作电压2.5~3.6V),因此,电源芯片的工作电压较低。

MOS管具有很低的导通电阻,消耗能量较低,在目前流行的高效DC-DC芯片中多采用MOS管作为功率开关。但是由于MOS管的寄生电容大,一般情况下NMOS开关管的栅极电容高达几十皮法。这对于设计高工作频率DC-DC转 换器开关管驱动电路的设计提出了更高的要求。

在低电压ULSI设计中有多种CMOS、BiCMOS采用自举升压结构的逻辑电路和作为大容性负载的驱动电路。这些电路能够在低于1V电压供电条件下正常工作,并且能够在负载电容1~2pF的条件下工作频率能够达到几十兆甚至上

- 电容降压LED驱动电路(06-24)

- 新型大功率蓝光LED光源驱动电路设计(08-03)

- 电动自行车控制器MOSFET驱动电路的设计(11-18)

- 两种常见的MOSFET驱动电路设计(12-02)

- 大功率LED恒流驱动电路的设计实例(06-06)

- 高频逆变电源的保护与驱动电路的设计(06-26)