在使用负载开关时,时序决定一切!

对于一个终端用户来说,打开一个电子设备很简单;只需按下按钮就可以了。然而,需要花费大量的精力来创建一个平滑顺畅的加电体验。系统接通的过快将会导致由不可控的涌入电流大尖峰所引起的电源故障。对于那些基于微处理器或FPGA的应用来说,正确的运行需要特定的电源轨排序。有时候,在启用下游电路之前,最好让特定的子系统加电。使用负载开关来管理电源排序可以更轻松地为终端用户提供平滑顺畅的加电体验。

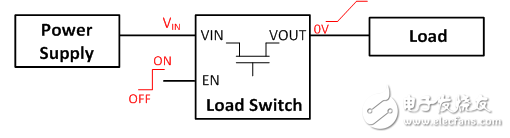

在大多数系统中,在一个设计中遍布着电容器,以确保不会出现电源轨压降。在最开始加电时,为这些电容器充电会导致涌入电流;而这个涌入电流会超过下游电路的最大电流额定值。如果听之任之,这会使得电压轨处于稳压之外,从而使系统进入不利的状态。不对涌入电流进行检查和限制也会损坏电路板连接器和电路板迹线,这是因为涌入电流超过了它们的承载能力。为了管理涌入电流,施加到电容负载上的电压需要具有一个受控的上升时间。所有德州仪器 (TI) 负载开关都具有一个集成软启动,而某些器件甚至提供针对变化电容负载的可调上升时间。图1显示的是这个集成软启动。

图1:一个为系统负载提供受控上升时间的负载开关

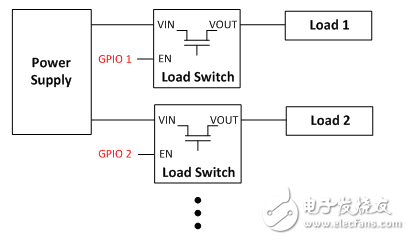

在电源和电容负载之间放置一个负载开关能够极大地降低接通/启用负载时的涌入电流。很多处理器和FPGA具有非常明确的电源排序要求,以及一个特定的电源轨接通顺序。负载开关使满足电源排序要求变得更加简单,从而实现针对每个电源轨的负载点控制。那么,为每个电源轨供电就简单到只需将正确的GPIO信号发送给正确的负载开关。图2显示了这个概念。

图2:为每个负载使用单独GPIO的电源排序

某些负载开关甚至具有一个电源正常 (PG) 信号;这个信号表示输出何时完全接通。通过将PG信号接至序列中下一个负载开关的启用引脚,对于所有电源轨来说,电源排序就只需要一个GPIO信号了。图3显示了这个配置。

图3:无需GPIO信号的电源排序

负载开关对于系统断电同样有效。负载开关的下降时间由输出负载对其电容的放电速度决定。为了加快这个放电过程,并且确保一个0V状态,某些负载开关具有一个快速输出放电 (QOD) 特性,如图4所示,这个特性通过一个内部电阻将输出放电至接地电平。

图4:一个支持QOD的负载开关

不论系统是加电还是放电,负载开关都能使时序和排序要求简单到按下一个按钮即可完成。

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)