基于FPGA的速率自适应图像抽取算法

6 b,格式定义见表1.

附加信息与数据一起被存到存储芯片中。在回放时,读取附加信息,解析出高VCDU有效/无效信号和低VCDU有效/无效信号。由回放请求模块进行数据滤除,保证仅回放有效数据,并且为完整图像。

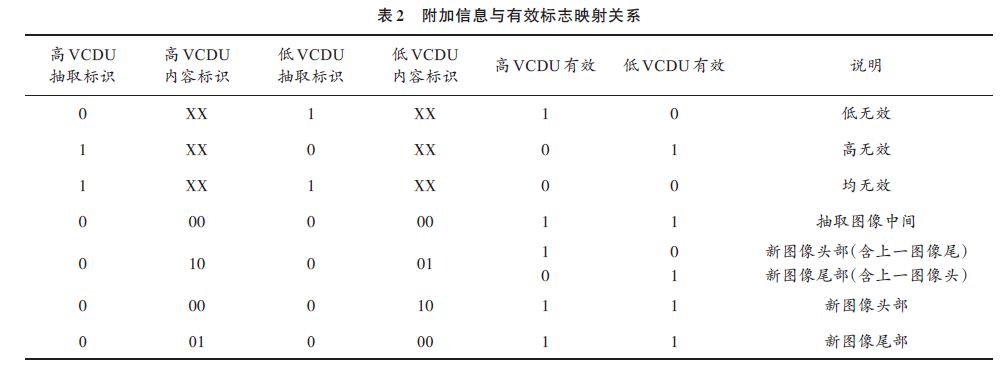

附加信息与有效标志映射关系见表2.对输入数据的各种情况,按照表2中映射关系解析出有效/无效信号。

数据过滤模块设置缓存,根据高低VCDU有效标示控制缓存地址,为1进行读取,为0跳过无效的VCDU数据,实现数据的滤除。

1.2 实时性设计

方法中必须获取到帧头VCDU 信息和帧尾VCDU信息才会更新图像数据帧地址寄存器,即在收到一整幅图像之后才能进行回放。

抽取的延时计算一幅图像第一比特输出和输入时间之差,最坏情况时第N 幅图像已经写入,第N + 1 幅图像尾部没有写完,即在第N 幅图像头写入后两幅图像时间才开始回放。抽取过程中延迟时间=两幅图像时间+数据回放时间。工程中,图像生成速率为10幅/s,一幅图像的生成时间按 100 ms计算。

回放数据的时间为数据从FLASH芯片中读出时间和数据缓存时间,每页2 KB,读取时间约320 μs;其余处理路径上的寄存时间《10 μs.因此,抽取过程中延迟时间约为200.33 ms ,完全可以满足图像的回放观看需要。

1.3 速率自适应设计

图像抽取的比例(即抽取图像的间隔)与输入速率和回放速率相关,在工程应用中,输入图像速率为 13.33 Mb/s,回放速率为50 Kb/s,其中图像有效数据率为41.808 Kb/s,一幅图像大小为131 080 B,每幅图像形成149个VCDU帧,下行共149&TImes;1 024 B=152 576 B.

以50 Kb/s 速率进行回放,回放一幅图像需要152 576&TImes;8/41 808=29.19 s,此过程中记录图像29.19&TImes;10=291.9,约292帧,即间隔约292帧抽取一幅图像。

实现速率自适应的关键是抽取方法的各个环节和输入速率、回放速率均没有耦合。

输入数据通过帧头尾识别,划分为标识出头尾的VCDU,输入数据速率改变,仅影响VCDU 的数据间隔。

VCDU 的数据间隔实际影响写控制模块对FLASH 芯片操作的频繁程度。因此在输入速率符合入口速率的要求时,数据可以被正常存储并产生附加信息,输入速率对方法没有影响。

回放数据从FLASH读出后,解析附加信息,进行缓存、滤除无效数据后输出回放。回放速率的改变,将导致回放控制模块加载头尾寄存器的间隔改变。回放速率减慢,加载间隔增长,头尾地址寄存器将被写控制模块刷新多次,即抽取图像的间隔自动增大。回放速率加快,加载间隔减小,由于在算法设计中考虑只有新的头尾地址被存入时,回放模块才能正确加载新地址,否则回放模块会停止在当前地址继续等待新图像。因此抽取图像的间隔会自动减小,当没有新图像时,抽取模块会等待新数据进入。

速率的自适应有利于算法的稳定性和通用性,在输入、回放速率改变时不需要改变抽取程序即可实现抽取回放功能。

2 工程实现与验证

在工程中采用Xilinx 公司300 万门FPGA,XQR2V3000[10]进行实现,占用资源(Slices)27%,经仿真和测试验证满足需求。

2.1 仿真情况

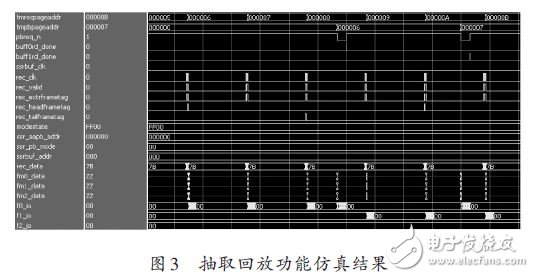

FPGA仿真情况如图3所示,在抽取回放过程中,回放指针关系正确,间隔相等,符合分析情况。

2.2 工程验证情况

在下行速率50 Kb/s时,按前述计算,间隔292帧抽取一幅图像。实际测试中,抽取图像均为整幅图像帧,且两幅图像之间连续,抽取的图像号为 0,291,581,872,1 167,1 457,1 749,2 040,2 334,2 627,2 917,3 209,3 500,3 793,4 083,4 377,4 668,4 961,5 251,5 543,5 837,6 128,6 421,6 711,7 003,图像号、图像间距的测试结果与理论值对比如图4(a),(b)所示,实际测试图像间隔与计算值符合,误差小于3幅图像。

在下行速率250 Kb/s时,有效数据率为241.808 Kb/s,按上文计算方式计算,间隔约50帧抽取一幅图像。实际测试中,抽取图像均为整幅图像帧,且两幅图像之间连续,抽取的图像号为 0,50,100,151,201,251,302,353,403,453,504,555,605,655,706,757,807,857,908,959,1 009,1 059.图像号、图像间距的测试结果与理论值对比如图4(c)、(d)所示,实际测试图像间隔与计算值符合,误差小于1幅图像。

两种速率下,实际测试图像间隔与计算值符合,验证了方法的功能性能符合需求,且具有速率自适应特点。

3 结语

本文设计实现了一种速率自适应的载荷图像抽取方法,适用于深空探测器载荷自主管理和地面可视化应用,实现了完整载荷图像实时抽龋采用FPGA实现算法,经过测试,抽取图像

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)