基于AMBA-AHB总线的SDRAM控制器设计方案

制寄存器的信号解码并寄存,传送已经解码的NOP、WRITEA、READA、REFRESH、PRECHARGE 和LOAD_MODE命令和ADDR给命令解析模块。

控制接口模块还含有一个用于给命令解析模块产生周期刷新命令的刷新电路,用于给命令模块发送刷新请求。收到命令模块的刷新请求后,减法计数器重新装入数值,重复以上过程。

本设计所使用的MT48LC16M4A2 型号SDRAM 存储器具有每64 ms刷新4 096次的要求,因此由64 ms/4 096=15.625 09 μs知,器件必须至少每15.625 09 μs刷新一次。假如存储器和SDRAM控制器工作在100 MHz的时钟周期下,那么刷新间隔周期的最大数值是15.625 μs/0.01 μs=1 562 d.

4.3.2 命令解析模块

命令解析模块接收控制接口模块输出的已经解码的命令和周期性输出的刷新请求,产生合适的命令给SDRAM器件。从刷新控制逻辑电路发出的刷新请求比主机接口的命令的优先级别高,因此模块还含有一个简易的仲裁电路,用于仲裁主机的命令和刷新控制逻辑所产生的刷新请求。

在仲裁电路已经接受主机命令后,命令被送到模块的命令发生器部分,命令模块使用3个移位寄存器来产生命令之间的时序,一个移位寄存器用于控制ACT 命令;第二个用于控制读或写命令发出的时间;第三个用于对命令的持续时间定时,这样仲裁其就可以判断最近请求的操作是否已经完成。

命令解析模块所产生的输出信号OE用于控制数据通路模块的输入数据通路的三态缓冲。

4.3.3 地址数据复用总线模块

该模块实现SDRAM的地址复用,地址的行部分在ACT(RAS)命令时复用到SDRAM输出的A[11:0],地址的列部分在读(CAS)或写命令时复用到SDRAM地址线上。

4.3.4 数据通路模块

数据通路模块提供了SDRAM和主机之间的数据接口,负责SDRAM控制器与外部SDRAM存储器之间的数据交换,具体说就是在对SDRAM写操作时将来自AHB总线的数据放到外部数据线上,在对SDRAM读操作时,将来自SDRAM的数据正确送到AHB总线上。

5 设计实现与仿真结果

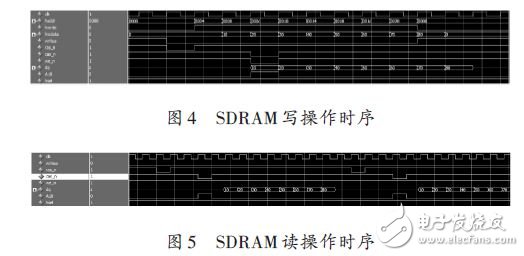

本文使用Micron 公司提供的型号为MT48LC16M4A2 的Verilog 仿真模型进行仿真验证,证明了设计的正确性。仿真结果如图4,图5所示,图4是SDRAM写操作的仿真时序图,即将AHB总线控制操作转化成SDRAM 写操作指令;图5 表示的是将写入SDRAM的数据连续读出的仿真时序。

6 结语

本方案设计了一个基于AMBA-AHB 总线的SDRAM控制器,将AMBA-AHB 总线的控制操作转化成了符合SDRAM 操作规范的控制指令,最后的仿真波形证实了该设计的正确性。

- 基于SDRAM文件结构存储方式的数据缓存系统(09-08)

- 基于SDRAM文件结构存储的数据缓存系统FPGA实现(10-25)

- 高分辨率视频图像处理中SDRAM控制器的设计(02-10)

- 高速图像处理系统中DDR2-SDRAM接口的设计(06-23)

- SRAM简介及与DRAM/SDRAM的比较(07-25)

- DRAM SRAM SDRAM内存精华问题汇总(10-13)