基于FPGA多路机载冗余图像处理系统的设计方案

摘要:本文以FPGA作为核心处理器,提出了一种基于FPGA多路机载冗余图像处理系统的设计方案,实现了对多路DVI视频冗余信号的解码、编码、实时处理以及输出显示,并且信号通道增加冗余设计,因而加强了系统的稳定性和可靠性。方案中的电路设计简洁,具有较强的灵活性和扩展性。通过实际测试结果表明,系统能够流畅地对1 600×1 200分辨率,60 Hz刷新率,24位真彩色的高清视频进行实时处理,其系统可靠、稳定,实用性强。

0 引言

DVI(数字视频接口)是当前数字显示领域研究和应用的热点,面向DVI输出的视频处理技术不仅解决了显示器高分辨率、高刷新率等问题,而且提高了稳定性和显示性能,并进一步降低了平板显示器的成本。因此,面向DVI输出的视频控制器的研究具有十分重要的现实意义。

根据DVI标准,一条TMDS通道可以达到165 MHz的工作频率和10 b 接口,也就是可以提供1.65 Gb/s的带宽,这足以应付1 920×1 080@60 Hz(23寸LCD)的显示要求。另外,为了扩充兼容性,DVI还可以使用第二条TMDS通道,这样其带宽将会超过3 Gb/s.也正是由于其较高的带宽优势,目前DVI已经成为了IT业界最具前途的规范。

DVI具有支持高带宽数据传输和高清晰图像显示的优点。模拟视频的显示是通过数字到模拟到数字的转化实现的,而DVI接口无需进行这些转换,直接数字到数字,避免了信号转换而带来的图像质量损失,使图像的清晰度和细节表现力都得到了大大提高。基于以上优点,DVI接口被广泛应用于航空、航天等领域。

1 总体方案设计

1.1 总体方案原理框图

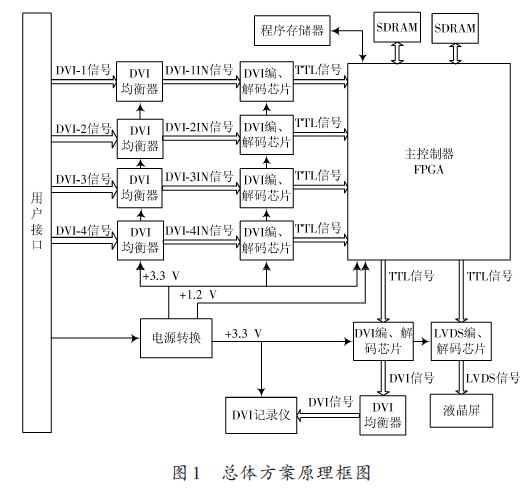

用户输入4路DVI信号,然后根据输入信号特性进行选择,将视频信号实时显示在液晶屏上。另外,将实时显示的图像回送给记录仪,此时记录仪实时记录当前的信息以及故障信息,确保在全任务阶段图像显示的正确性。根据设计要求,选择Altera公司生产的 FPGA 芯片EP2S30F1020I4 为主控芯片,配置芯片选用EPCS16SI16N.利用FPGA内部丰富的逻辑资源和强大的IP核,配以相应的外部电路,构建出一个灵活、简洁、可靠的机载视频图形处理系统的嵌入式硬件模块。其总体方案原理框图如图1所示。

1.2 DVI编解码设计

在很多设计中,设计人员为了方便,简化电路,可能不会增加均衡器,对输入信号不进行处理。从而在后期的产品试验过程中,很容易就会出现信号显示质量差,兼容性差的缺陷,导致整个产品重新设计或整改,延缓了产品交货进度。根据用户输入的视频特性,本文采用均衡器+DVI编、解码器的方式,对输入、输出信号进行转换处理。这样处理有如下优点:传输距离较长,信号干扰小;外围电路简单,设计灵活、可靠;系统速度快、灵活性强、功能可扩展,系统兼容性好。

在本系统中,选用TI 公司生产的均衡器DS16EV5110,该器件具有功耗低、体积小、外围电路简单等特点。另外,DVI编解码芯片选用TI公司生产的芯片TFP401和 TFP410,同样具有功耗低、体积小、外围电路简单等特点。该器件控制引脚直接连接至FPGA,可以很好控制这些器件的工作状态,以便减小功耗。并且,整个FPGA内部逻辑控制简单、可靠。

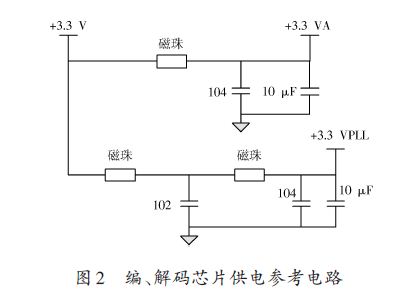

在硬件电路设计中,还需要考虑高频特性对信号的影响。整个系统显示的分辨率为1 600×1 200@60 Hz,信号位为真彩色24 b,采用奇偶方式,参考时钟162 MHz,DVI编码时钟为10×162 MHz=1.62 GHz,其编码码元理论宽度仅为t = 1 1.62 Hz=0.62 ns,则码元的最大变化时间应在0.62 4 = 0.16 ns之内。考虑数据传输的可靠性和稳定性,采用双像素传输,可以大大降低信号采样频率。此外,还要考虑到PCB布局地线的完整性和供电去耦特性。其编解码芯片混合信号的供电参考电路如图2所示。

2 SDRAM 视频缓存设计

2.1 SDRAM选择依据

整个系统显示的分辨率为1600×1200@60 Hz,信号位为真彩色24b,则一帧图像所需需要存储的容量C = 1 600×1 200×24=46 080 000 b≈47 Mb;考虑到SDRAM乒乓操作和容量等问题,选用MICRO公司生产的容量为128M的MT48LC4M32B2TG-6器件,速度等级6,时钟频率达到166 MHz.该器件具有32根数据线和12根地址线,还有一些控制线。通过在FPGA内部搭建逻辑控制单元,可以很好的控制SDRAM 视频信号的翻转等操作。

2.2 FPGA内部原理逻辑框图

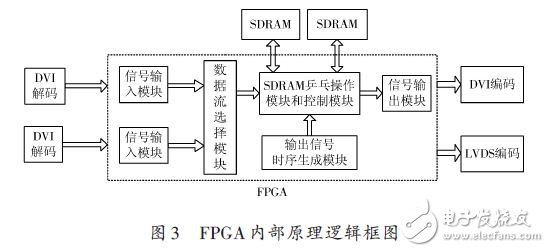

FPGA内部原理逻辑框图如图3所示。

2.2.1 FPGA内部逻辑功能介绍

(1)信号输入模块

这部分的主要功能是接收外部输入的视频信号,增强输入信号的驱动能力,为信号的后续处理做准备。其用Verilog 语言实现的逻辑

- 基于SDRAM文件结构存储方式的数据缓存系统(09-08)

- 基于SDRAM文件结构存储的数据缓存系统FPGA实现(10-25)

- 高分辨率视频图像处理中SDRAM控制器的设计(02-10)

- 高速图像处理系统中DDR2-SDRAM接口的设计(06-23)

- SRAM简介及与DRAM/SDRAM的比较(07-25)

- DRAM SRAM SDRAM内存精华问题汇总(10-13)