高速图像处理系统中DDR2-SDRAM接口的设计

文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现。

1 DDR2-SDRAM控制器的操作原理与设计

1.1 DDR2-SDRAM的操作原理

DDR2 SDRAM是运用DDR结构来达到高速操作。本文采用的DDR2-SDRAM是Micron的MT4H3264HY-53ED3。这款DDR2的存储空间为256 MB,由4片容量为512 Mb的内存芯片构成。每个芯片的数据位宽为16 b,有4 bank,13条行地址线,10条列地址线,因此每个内存芯片容量为8 192×

1 024×4×16 b,即512 Mb。4片组成起来就构成了MT4H3264HY-53ED3的64 b位宽。

DDR2 SDRAM的操作主要通过以下控制信号给出:行地址选择信号( ),列地址选择信号(

),列地址选择信号( ),写使能信号(

),写使能信号( ),时针使能信号(CKE),片选择信号(

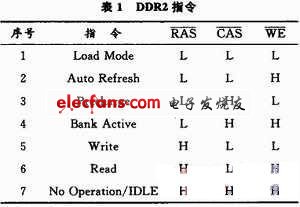

),时针使能信号(CKE),片选择信号( )。各种指令不同的组合方式完成不同的功能。表1为各种指令完成的组合方式。

)。各种指令不同的组合方式完成不同的功能。表1为各种指令完成的组合方式。

1.1.1 Load Mode指令

用来配置DDR2内存的模式寄存器,包括一个主模式寄存器及3个扩展模式寄存器,它们被用来设定内存的工作方式,包括突发长度的选择、突发的类型、CAS延迟、CAS附加延迟、DLL使能、ODT设置、OCD设置以及DQS设置等。

1.1.2 Precharge指令

预充电指令是用来重新激活bank中已经打开的行。在预充电指令发出后,当前bank必须等待一个特定的时间(tRP)后才可以再次激活。

1.1.3 自动刷新指令

DDR2 SDRAM内存需要每7.8μs刷新一次。自动刷新不需要外部提供行地址信息,DDR2 SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中所有的存储体进行,所以无需列地址。在进入自动刷新模式前,所有的bank必须都处于预充电状态,自动刷新指令在预充电指令后延迟tRP才能给出。

1.1.4 Active指令

Active用来激活bank中的某一行。在对DDR2内存进行读/写之前,都必须执行该指令把bank中的某一行激活。激活命令到读/写命令之间的最小延迟由AL决定,当AL为0时,最小延迟由tRCD(RAS to CAS delay)决定。当AL不为0时,激活命令到读/写命令之间的最小延迟就可以不受tRCD限制,读/写命令可以提前,但其实最后数据的读/写并不提前,这样可以提高总线的利用率。

需要注意的是,当要激活同一bank中不同的行时,必须先对原来激活的行进行预充电,才能激活新的行。同一bank中连续的active命令之间的间隔必须受tRC(RAS cycle time)的控制。

1.1.5 Read指令

读指令是用来对DDR2内存进行读操作,并对突发读进行初始化。其中BA0和BA1给出bank地址,A0~A1给出起始列地址。突发读结束后,激活的行在预充之前继续保持有效,直到该行被预充电。从列选择到数据输出的延迟为CAS延迟(CL),整个读延迟等于AL+CL。读操作时由内存给出一个与数据同步的数据滤波信号DQS,它的边沿与读取的数据边沿对齐。

1.1.6 Write指令

Write指令用来控制DDR2内存进行写操作,并给出burst写的起始地址。其中BA0和BA1给出bank地址,A0~A1给出起始列地址。整个写延迟为读延迟减去一个时钟周期,即写延迟等于AL+CL-1。写操作时,控制器同样给出一个与数据同步的数据滤波信号DQS,它的边沿与写数据的中间对齐。

1.1.7 Idle指令

用来使DDR2内存处于空闲无操作状态。

1.2 DDR2-SDRAM控制器的设计

本文中的DDR2 SDRAM控制器是采用VHDL硬件描述语言设计的,主要由4部分组成:用户界面模块(User Interface)、基础模块(infrast-ructure)、物理层模块(Physical layer)和存储控制模块(Controller)。DDR2-SDRAM控制器的设计原理框图如图1所示。

时钟生成模块用来产生控制器中所有模块的时钟信号。外部用户时钟通过数字时钟管理器(DCM)进行处理后,输出0度和90度的时钟。同时该包括了一个延迟校准模块,是用来校准读数据(DQ)对读数据选通脉冲(DQS)的延迟,以便DQS的边沿能正确对齐DQ有效窗口的中间位置。

用户接口模块主要包括读/写数据和地址三类FIFO,用来接收和存储用户的数据,命令和地址等信息,起到缓冲和同步数据的作用。控制器模块生成该模块所需要的控制信号。

物理层模块负责在控制信号的约束下完成用户访问地址与访问指令的解释与匹配,产生DDR2 SDRAM所需的控制指令信号,并保证指令与地址,数据的同步和信号的维持。

控制模块主要实现的功能为:在系统上电过程及系统意外复位发生时,与初始化模块配合,对控制器和所控制的DDR2进行初

- 基于USB2.0和DDR2的数据采集系统设计(03-19)

- DDR2和DDR3内存的创新电源方案(06-11)

- 基于CYUSB3014 USB3.0总线开发技术(02-25)

- P51XA单片机与图形液晶显示器的接口设计(08-27)

- 基于AT25T1024 FLASH的高速SPI接口设计(06-04)

- 借助JTAG接入经验,可推动设计向新一代发展(07-15)