高速图像处理系统中DDR2-SDRAM接口的设计

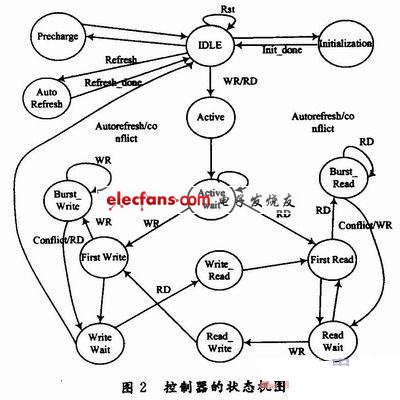

始化设置,复位延时保护等:在系统正常工作时,进行系统读/写请求指令的接收、应答,对系统访问地址的采样与同步,完成所需的所有状态转换、任务调度、总线仲裁、时序同步,并为用户接口模块、物理层模块产生相应的控制信号,为系统提供控制器状态指示信号。控制器的状态机结构如图2所示。

2 图像处理系统中DDR2接口的设计

DDR2作为整个图像处理系统的缓存,起着至关重要的作用。它将外部输入的图像按帧存入DDR2中,然后按帧将图像数据送到外部继续处理。基于单片FPGA的控制逻辑所需要完成的功能可以简单的概述如下:

(1)接收来自外部的图像数据,并进行缓冲和数据重排,产生符合DDR2-SDRAM控制器位宽的数据信号。

(2)产生对DDR2-SDRAM的读/写命令和地址,并将它们寄存在FIFO中,随时供DDR2控制器提取,因此系统需要一个地址产生逻辑。

(3)对DDR2-SDRAM进行直接控制,将用户产生的地址命令进行解析,产生读/写、刷新等一系列操作,对DDR2-SDRAM发出的各种命令要符合特定的时序要求。在上电的时候还必须完成对DDR2-SDRAM的初始化工作。

(4)建立用户与DDR2-SDRAM的数据通道,在DDR2-SDRAM和用户接口之间传递需要写入或者读出的数据,并且调整对应读/写操作的DQS信号时序,使其满足DDR2-SDRAM的要求。

(5)缓存从DDR2-SDRAM中读出的数据,由于直接读出的速度非常高,直接处理会对后端产生很大的压力,因此需要进行缓存之后才送到后续处理。

由上面的描述可以看出,控制逻辑所要完成的功能是相当复杂的,因此我们采用模块化的设计方案。

2.1 时钟生成模块

时钟生成模块主要负责整个系统的所有时钟,包括DDR2控制器所需要的时钟,外部图像所需的时钟。全部由DCM来产生。

2.2 数据接口模块

数据接口模块主要是负责不同数据之间格式的转换,这个模块主要是考虑到输入端的数据的不同格式,必须经过格式转换才能符合DDR2位宽的数据。

2.3 输入/输出缓存模块

输入/输出缓存模块是采用V5器件的DRAM来实现FIFO的,输入缓存是由两个DRAM来完成的,DRAM配置为12×1 024,12为数据宽度,1 024为存储深度,这个配置是根据具体图像的位宽和每行的像素点来设定的。在这里暂定的图像源是标准的VGA图像,其大小为800×600。数据源每写入一行数据(800个数),然后读出一行数据。考虑到系统的稳定性,采用两个FIFO交替的读/写数据,也就是所谓的乒乓操作,,当一个FIFO在读时,另一个FIFO就写,然后交替读/写。在每一个FIFO读完数据后,对其清零。这样就保证每一次写入的数据不相互干扰,保证了系统的稳定性。其中的输入/输出选择单元是通过判断VGA图像的行数来判断写和读哪个FIFO的。

除了缓存数据,FIFO在本模块的另一个重要的作用就是时钟域的转换。外部的输入数据和输出数据的时钟都是40 MHz,而DDR2的读/写数据时钟是100 MHz的,这样就存在着时钟域的转换问题,由于FIFO的读/写可以用不同的时钟。在输入端,就可以用40 MHz的时钟把数据写入FIFO,然后用100 MHz的时钟从FIFO读出数据。在输出端可以用100 MHz的时钟把从DDR2读出的数据送入FIFO,然后再用40 MHz的时钟从FI-FO中读出数据,送到VGA显示。但是由于读入与写出的时钟频率不一样,很容易出现FIFO读空和写满的问题。该问题的一般解决方法是利用FIFO的ALMOSTFULL和ALMOSTEMPTY来解决。在这个系统中,考虑到输入的数据源和VGA显示的时钟频率都是40 MHz,所以采用VGA数据有效信号来控制FIFO的写,行消隐信号来控制输入FIFO的读,即每来一行数据才读一行数据,这样就保证了输入FIFO不会读空。而输出FIFO的写是通过DDR2内部的读数据有效位来控制的,因为DDR2内部的操作是写1行,读1行,所以在写入FIFO一行数据后,要等到下一行到来后,才会往输出FIFO写入数据,所以也就解决了输出FIFO写满的问题。

2.4 DDR2-SDRAM控制模块

DDR2-SDRAM的读/写控制是整个系统的关键。由于要缓存图像,所以就必须在DDR2里面开辟两个大小相同的存储单元。这两个存储单元的大小是根据一帧图像的大小来开辟的,其大小为800×600个存储单元。对DDR2的存储操作为先向第一个存储单元写入第一行数据,读出第二个存储单元的第一行数据。当写满第一个存储单片后,第二个存储单元也被读空,这时候交换读/写地址,读一个存储单元,写第二个存储单元,依次轮换。

由于图像数据具有消隐时间,我们可以在场消隐的这段时间里来交换读/写地址。

3 实验结果

为了测试基于DDR2的图像存储性能,外部输入图像

- 基于USB2.0和DDR2的数据采集系统设计(03-19)

- DDR2和DDR3内存的创新电源方案(06-11)

- 基于CYUSB3014 USB3.0总线开发技术(02-25)

- P51XA单片机与图形液晶显示器的接口设计(08-27)

- 基于AT25T1024 FLASH的高速SPI接口设计(06-04)

- 借助JTAG接入经验,可推动设计向新一代发展(07-15)