基于FPGA多路机载冗余图像处理系统的设计方案

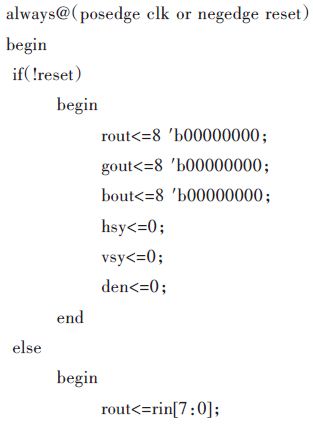

代码如下所示:

(2)数据流选择模块

根据需要选择两路输入视频信号中的一路进行输出。

(3)SDRAM乒乓操作和控制模块

由于SDRAM 乒乓操作具有节省缓冲区空间、流水线式算法以及低速模块处理高速数据流的特点。因此,本设计采用乒乓操作SDRAM.

SDRAM 作为整个图像处理系统的缓存,起着至关重要的作用。它将外部输入的图像按帧存入SDRAM中,然后按帧将图像数据送到外部继续处理。FPGA的控制逻辑所需要完成的功能有:接收来自外部的图像数据,并进行缓冲和数据重组,产生符合SDRAM控制器位宽的数据信号;产生对SDRAM 的读、写命令和地址,并将它们寄存在FIFO中,随时供SDRAM控制器提取。因此,系统需要一个地址产生逻辑;对SDRAM进行直接控制,将用户产生的地址命令进行解析,产生读/写、刷新等一系列操作,对SDRAM 发出的各种命令要符合特定的时序要求。在上电的时候还必须完成对SDRAM的初始化工作;建立用户与SDRAM 的数据通道,在SDRAM和用户接口之间传递需要写入或者读出的数据,并且调整对应读/写操作的DQS信号时序,使其满足SDRAM的要求;缓存从 SDRAM中读出的数据,由于直接读出的速度非常高,直接处理会对后端产生很大的压力。因此,需要进行缓存之后才送到后续处理。

(4)输出时序生成模块

这部分模块的主要功能是对SDRAM 进行操作,生成需要的视频时序信号以及生成驱动液晶屏的视频信号。

2.2.2 SDRAM操作

为了满足前后端数据流匹配,并实时发送,这里采用了SDRAM读写交替进行的读写方式。

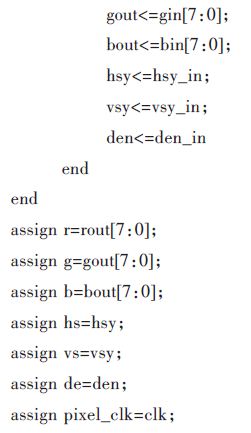

SDRAM 读到写时序图如图4所示。写入和读出操作的发起是由行激活命令开始的,命令为10011,发起的同时sdram_addr送入列地址,发起写入读出命令时送入行地址。写入命令与数据同步,读出命令在发出后潜伏期时间后送出数据到端口,sdram_data 为SDRAM 的输入输出数据端口。预冲方式采用了自动预冲,即在发起读写命令时将地址位A10置高就可以在读写操作后SDRAM内部自动进行预冲操作,不需要发出额外命令,自动预冲占用4个时钟周期。

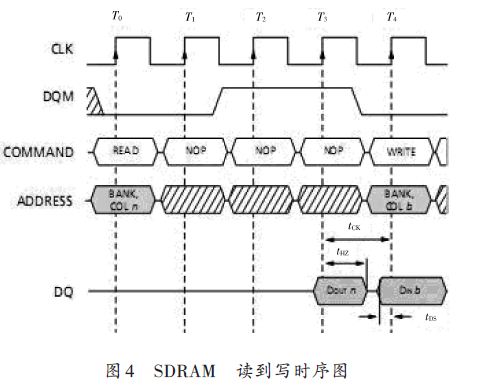

3 仿真分析以及测试结果

读写操作交替进行仿真图如图5所示。图5中包含了两个写入操作,一个读取操作。

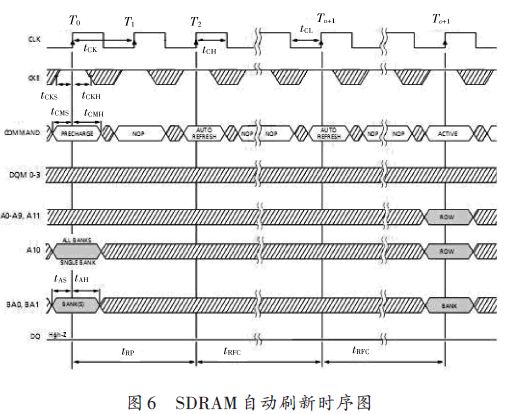

SDRAM在完成读写操作的同时还需要完成每64 ms全行(4 096行)自动刷新操作,为所有行进行充电,不然就会导致SDRAM内的数据丢失。自动刷新时序图如图6所示。

这里将自动刷新操作穿插在读写当中,经计算为15 μs 需进行一次自动刷新操作,通过一个计数器每15 μs 发起一次自动刷新请求,程序检测到自动刷新操作请求后进行自动刷新操作然后再进行读写操作,自动刷新操作占用10个时钟周期。图7为写和读之间穿插了一次自动刷新操作,操作命令为10001.

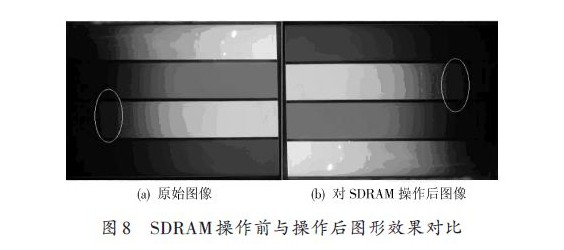

测试结果证明,该缓存系统实现了预定功能,可以对视频数据进行更方便的操作与管理。SDRAM操作前与操作后图形效果对比如图8所示。

4 结语

本文介绍了某机载实时冗余视频图形处理系统的设计方案,该系统利用FPGA设计结构化状态机实现对 SDRAM的控制,完成了对数据的缓存设计,实现了对多路DVI视频冗余信号的解码、编码、实时处理以及输出显示。该系统电路设计简洁,具有速度快、可靠性高、灵活性强和功能可扩展等优点。并且,由于信号通道增加冗余设计,因而加强了系统显示的稳定性和可靠性。本系统已经投入使用,其性能可靠、稳定,实用性强。该方法值得推广。(作者:赵小珍,刘波,朱标,陈文明)

- 基于SDRAM文件结构存储方式的数据缓存系统(09-08)

- 基于SDRAM文件结构存储的数据缓存系统FPGA实现(10-25)

- 高分辨率视频图像处理中SDRAM控制器的设计(02-10)

- 高速图像处理系统中DDR2-SDRAM接口的设计(06-23)

- SRAM简介及与DRAM/SDRAM的比较(07-25)

- DRAM SRAM SDRAM内存精华问题汇总(10-13)