来自凌力尔特的LTC4366高压浪涌抑制器应用深入讲解

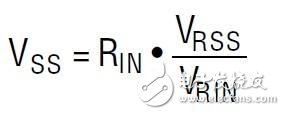

SS的阻值减小至上述"最小电源电压启动"中所规定的最大值以下。RSS中的电流超过了由VSS引脚所供应的电流(本质上IRIN)时,电容器C1开始充电。IRIN=IRSS时VSS引脚上的电压现在被标记为VSS(MATCH)。VSS引脚电压是一个位于RIN和RSS之间分压器的中点电压(在把VDD至VSS的齐纳箝位电压从电源电压减去之后)。

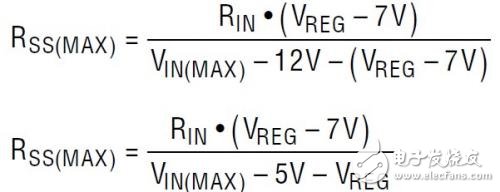

当VIN增加时,VSS(MATCH)电压增加。如果匹配电压超过了过压调节点(VREG),则负载不受保护。情况的确如此,因为C1在VSS已经超过VREG时仍将需要充电至2.55V。由于OUT引脚电压至少比VSS高2.55V,因此它超过了规定的最大值。应选择充分低于VREG(至少要低2.55V)的匹配点(在电源电压处于最大值的情况下),从而允许C1及时充电以保护负载免遭过压的损坏。实际上,使VSS引脚电压比VREG低7V可为C1的充电提供所需的裕量。

VSS(MATCH)(MAX) = VREG–7V

增加RSS将提高匹配点,因此确定最大RSS同时仍然提供针对过压的保护是有益的。采用IRIN=IRSS:

采用:

RSS = VSS(MATCH)(MAX) = VREG – 7V

RIN = VIN – VZ(VDD) – VRSS

代入:

如果我们保证RSS《RSS(MAX),则下式成立:

VSS(MATCH) 《 VSS(MATCH)(MAX)

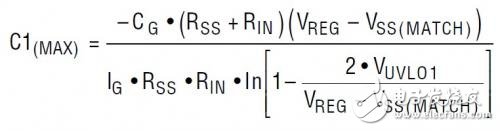

C1负责对充电泵进行旁路,且数值至少必需为0.22F。C1的尺寸也需要加以限制。栅极电容器(CG)决定了最大输出电容器C1(MAX),以将在OUT电压超过过压门限之前充电至2.55VUVLO1门限(VUVLO1)。

在大多数场合中:

C1(MAX)=10•CG至100•CG

GATE电容器,CG

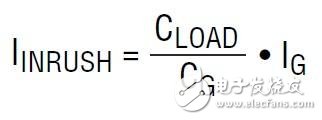

栅极电容器用于实现三项功能。第一:CG负责吸收过压瞬变期间来自MOSFET栅极至漏极电容的电荷。第二:该电容器还充当过压调节放大器的一个补偿组件。用于保证稳定性的CG最小值为2nF。最后,CG可设定GATE和OUT引脚的电压变化速率。GATE引脚电压的上升斜率等于20A/CG。该斜率决定了流入负载电容器的充电电流。

CG的额定电压必须大于调节电压(VREG)。

MOSFET的选择

LTC4366驱动一个N沟道MOSFET以传导负载电流。MOSFET的重要特性是接通电阻RDS(ON)、最大漏-源极电压V(BR)DSS、门限电压和SOA。可容许的最大漏-源极电压必须高于电源电压。如果输出短路到地或者在过压过程之中,则整个的电源电压将出现在MOSFET的两端。

MOSFET的门限电压在最小电源电压启动计算中使用。对于采用低于12V电源的应用,需要一个逻辑电平MOSFET。如果所用的电源高于12V,则使用一个标准门限N沟道MOSFET就足够了。

MOSFET的SOA必须包含所有的故障状况。在正常操作中,传输晶体管完全导通,因而耗散极少的功率。但在过压故障期间,GATE引脚电平被维持以通过MOSFET调节输出电压。大电流与MOSFET两端的高压降在这些场合中可以共存。必须将MOSFET的SOA曲线与故障定时器电容器的选择一道加以审慎的考虑。

布局考虑

由于SD、VDD和GATE引脚上具有高阻抗,因此这些引脚对于至地漏电流很敏感。例如:SD引脚上的至地漏电流若大于1.6A,则将启动停机状态。提供远离接地走线的足够间距并在裸露引脚上添加敷形涂层材料可降低漏电流中断系统操作的风险。应把旁路电容器C1布设在尽可能靠近OUT和VSS引脚的地方,这一点很重要。将10Ω电阻器安放在尽可能靠近MOSFET栅极引脚之处。这将减少导致MOSFET自激振荡的寄生走线电容。

FB引脚在调节环路闭合时对寄生电容很敏感。这种电容性负载引起的后果之一是在过压调节期间产生输出振荡。建议将电阻器RFB1和RFB2布设在靠近器件引脚的地方,并最大限度地减小FB走线本身的尺寸。

- 全方位剖析LTC4366浪涌抑制器工作原理(06-27)

- LED 驱动器 IC 可为众多照明应用的发展起到引领作用(07-02)

- 新型汽车设计需要降压-升压型转换器(07-02)

- 高电压浪涌抑制器可确保电源浪涌期间的可靠操作(07-30)

- 从低至 1.5V 的输入进行转换以提供高达 15A 的输出,无需辅助偏置电源(07-30)

- 到处都可以使用的“绿色电源”(09-18)