基于CPLD的高速数据采集系统的实现

液压系统具有结构轻小、传动比大、运行平稳、易于实现无级调速和自动化等优点,已被广泛应用于工业生产的各个领域。但液压传动系统(特别是大型液压系统)也存在一些缺点。主要是结构复杂、其内部状态难以检测,给液压系统的状态监测和日常维护带来一定的困难。因此如何提取系统的特征信号。有效地对液压系统进行状态监测,及时发现故障和隐患,有着十分重要的工程意义。

目前国内专门针对液压系统的数据采集产品比较少,而且存在诸如采集参数选择不当或不够、采集速率偏低、未能准确反映液压系统的工作状况、接口不利于安装或传输速度太慢等问题。本文设计了一种基于CPLD(复杂可编程逻辑器件)+FX2(单片机CY7C68013)的便携式高速数据采集系统,采用了数据流驱动多模块并行技术和USB2.0接口。实践证明,该方案结构简单,成本低廉,实时同步采集和传输速度相当于DSP系列的数据采集产品。

1 设计思路

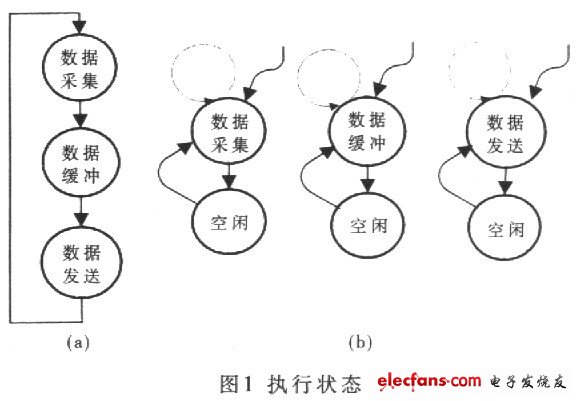

数据采集包括采集量到电参量的转换、信号调理、模/数转换、数据缓冲、数据发送等几部分。一般采用主控芯片直接控制模,数转换、数据缓冲、数据发送等模块顺序执行的方式,如图1(a)所示。要达到较高的采集速度,须使用如DSP等高速主控芯片,为此而增加了系统成本和软、硬件的调试难度。

本设计选用Cypress公司带智能USB接口引擎和4K FTFO的单片杌CY7C68013(FX2),其USB数据发送部分可独立自动执行。选用Altem公司的CPLD器件EPM7128,采用VefilogHDL语言编程,设计模/数转换、数据缓存集成控制电路。并采用数据流驱动多模块并行技术,当模块执行所需的数据满足条件时立即执行,三种模块可并行执行,如图1(b)所示,从而可通过低主频CPU来控制高速数据采集。

上位机软件采用美国国家仪器公司的IabVIEW语言编写。基于图形化编程的G语言使得上位机软件的开发效率大大提高。特别是其NI-VISA3.0(Virtual Instrumentation Software Arehitecture)控件的推出,可以通过调用其标准化面向具体功能的、通用仪器的API(Application Programmer Interface)驱动接口实现自主开发的USB设备的驱动。

2 硬件设计

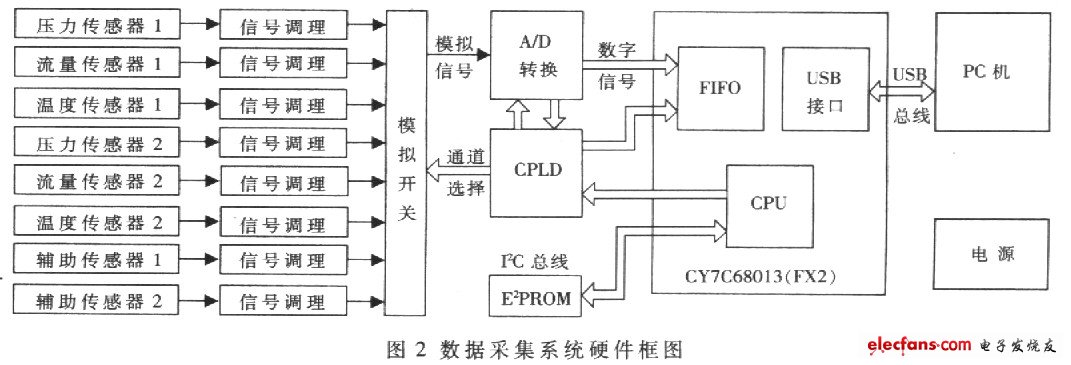

系统硬件配置如图2所示。液压系统中的压力、流量、温度以及振动频率等模拟量通过传感器变换为电信号后,经放大、缓冲、滤波等调理电路处理后,由模拟开关电路选择后送A/D芯片(AD574)转换成数字信号,并写入FX2内置的FIFO,由内部集成的uSB控制器自动发往上位机,完成数据采集。CPLD控制器除控制模拟开关电路和ADC(模,数转换电路)外,还控制将采集得到的数据写入FX2的FIFO。控制器设计采用数据流驱动多模块并行技术,以提高控制电路的执行效率。系统固件程序烧录于E2ROM中,通电或复位时,FX2自动加载。系统配备了直流电源,以满足室外便携采集的需要。

3 软件设计

3.1 CPLD程序设计

CPLD内含ADC采集控制和FIFO控制两个模块,A/D采集控制模块包括通道选择、转换时序发生和转换状态检测等部分,FIFO控制模块实现FIFO的写时序控制。FIF0写控制模块采用转换数据为触发条件,当A/D转换完成并把数据送到总线时,发出写FIFO触发脉冲,FIFO写控制模块将总线数据写入FIFO;A/D采集控制模块则以自身的采集数据状态和FIFO写完成作为执行条件。两个模块在单片机控制下并行执行,与此同时,当FIFO写满,智能USB控制器将FIFO内的数据发往上位机,实现了低主频CPU控制高速同步数据的采集和传输。由于USB控制器的传输率可高达480Mbps,采用两片FIFO缓冲,采集频率低于10MHz则可避免因uSB传输丢失数据。

3.1.1 A/D采集控制模块

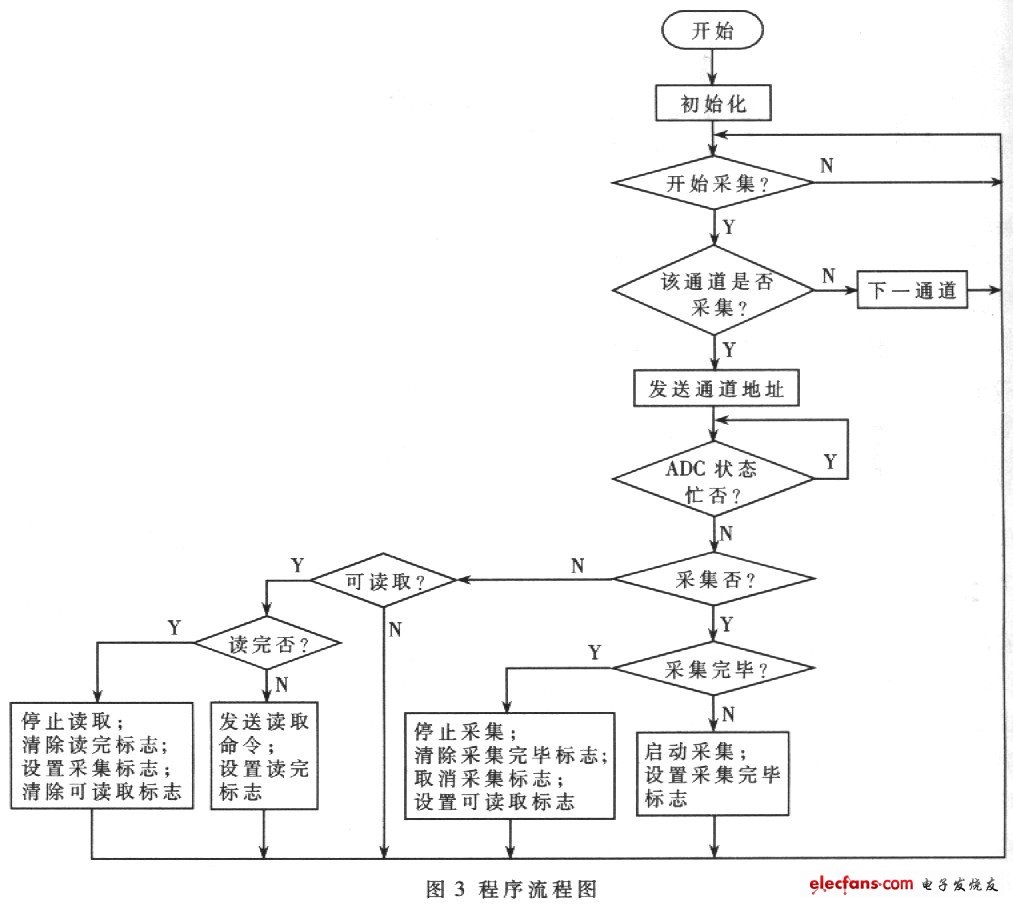

AD574独立操作模式(stand alone)工作时,通过R/C脚进行转换和读取控制,同时需要监控STATUS脚,在A/D芯片转换完毕后将12位转换数据并行输出到总线,同时输出写FIFO触发脉冲。图3所示为ADC控制器流程图,据此可设计相应的VefilogHDL程序。

3.1.2 FIFO控制模块

CY68013除自带USB2.0控制器外,还有一个4K×8b的FIFO,共分成4个端点,端点大小和缓冲层次可编程设置。本文设置成SLAVE FIFO工作模式,两个上传FIF0片(端点)。通过SLWR控制总线上的数据写入FIFO。当数据写满一片FIFO时,FIFO控制模块切换地址,以避免数据丢失,保证转换、发送的连续性。写满数据的端点由USB控制器自动发送。

如果在采集过程中FIFO控制器接到停止采集命令后,FIFO控制模块产生PKTEND信号,指示USB控制器将采集停止后未满FIF0中的剩余数据发往上位机。

3.2 底层固件及设备驱动

高速数据采集系统软件设计

- 基于CPLD的激光驱动电源的设计(08-26)

- 在CPLD基础上的电器定时开关控制系统设计(03-29)

- 基于DSP与CPLD设计智能变电站电网的IED(02-25)

- 基于ADSP-TS101S的多芯片数字信号处理系统的实现方案(02-11)

- 51单片机+CPLD让系统更高效(10-25)

- 基于CPLD的线阵CCD数据采集系统的开发(04-14)