51单片机+CPLD让系统更高效

一、引言

随着数字电子技术的发展,一种新的器件正在被广泛应用,那就是CPLD(ComplexProgrammable Logic Device) 复杂可编程逻辑器件,通俗的说就是可以把以上那些分离器件都放进去的一种可以二次开发的IC.基于此,本刊用这篇文章深入浅出的介绍一种采用51 单片机和CPLD 构建复杂电路系统的设计思想。

二、单片机系统中几个典型电路介绍

首先从熟悉的最小系统电路电路说起,如图1所示,图中用网络标号实现电路连接,这样绘制的电路图清晰整洁,U1 是经典的51 单片机 IC,复位电路和晶振电路是传统电路,这里C5 电容是靠近单片机VCC 引脚的,用来对电源滤波,图中其它芯片VCC 附近都有相同功能的滤波电容。U2 是经典的低八位地址锁存电路,这里的74373 也可以用74573 代替,U3 是地址译码电路,74138 实现连续8 个地址(1### #### #### #000 ~ 1####### #### #111,# 是无关位,可以是0 也可以是1,取决于电路其它部分的需要)对象扩展。

图1 MCU最小系统原理图

51 单片机给大家推荐STC 的89 或90 系列,其中90 系列已经有片内ADC 了,需要特别强调的是, 随着FLASH 技术的成熟,片内FLASH ROM从8K 到64K 任选,已经足够用了,所以现在很少有单片机系统外扩ROM 了,这样使得EA/VPP 和PSEN 引脚失去了原先的功能了,STC 的51 单片机已经将这两个引脚发展成P4 口了。

复杂的系统必然有很多输入输出接口,如图2所示,U5 是数据锁存器74273,扩展一个8bits 数据输出端口,U6 是三态数据缓冲器74573,扩展一个8bits 数据输入端口,分别用7432 实现读写时序接口匹配。

图2 MCU端口口扩展原理图

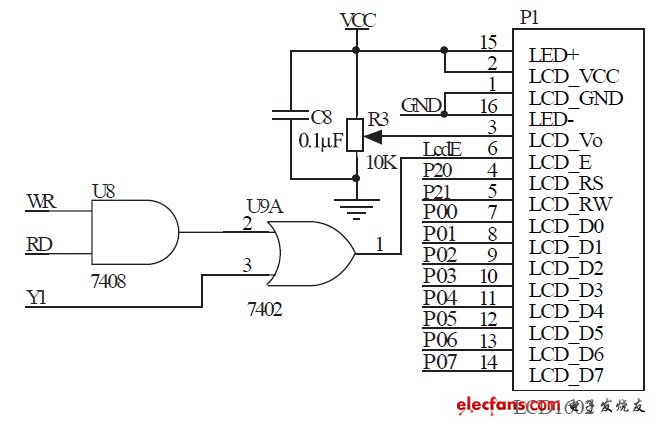

经典LCD1602 接口如图3 所示,这里7408、7402 逻辑门用来实现6800 时序(读写信号有独立接口的是8080 时序,这里只有使能信号E,需要外逻辑电路将读写信号相与合并使用)。

图3 LCD1602接口电路原理图

以上给出的系统还算不上是复杂系统,总共采用了8 块IC,一个实现特定功能的系统往往更复杂,需要采用的IC 会更多。能不能把这些分离的器件用CPLD 来实现呢?答案是肯定的。

三、单片机与CPLD接口设计

以上经典电路中,系统扩展使用了单片机总线模式,各个对象采用的三总线连接,根据这种电路结构,这里给出一种单片机同CPLD 的总线接口模式,如图4 所示。

图4 单片机与CPLD总线接口示意图

这里选择A l t e r a 公司早期的EPM7064SLC44-10 为例,这是很老的一款CPLD器件,是5V 供电。其实选择什么CPLD 型号并不是关键,关键是学习用CPLD 代替分立器件的思想和方法。数据总线P0 口同CPLD 一般IO 口相连,完成数据和低8 位地址传送;控制总线包括单片机读写控制信号Rd(P3.7) 和Wr(P3.6),以及地址锁存信号ALE(Address Lock Enable)和高位地址线A15(P2.7) 通过CPLD 的全局信号引脚输入,包括全局时钟输入:INPUT/GCLK1, 全局清零输入INPUT/GCLRn, 全局使能输入INPUT/OE1,INPUT/OE2, 这几个信号有专用连线与CPLD 中每个宏单元相连,保证信号到每个宏单元的延时相同并且延时最短。实际电路原理图如图5所示。

图5 MCU与CPLD接口电路原理图

这样一块CPLD 器件就代替以上除单片机外的7 块芯片了,在电路板上将节约大片的PCB 面积,好处还远不止这些,因为CPLD 是二次开发的,其内部电路可以根据需要再次设计,反复修改,极大的增加了电路设计的灵活性。

读者看到这里,肯定对自己动手设计CPLD 电路充满了期待,下面介绍如何借助工具软件开发CPLD 内部电路。

四、CPLD开发介绍

一般来说,CPLD 生产商都有配套的开发工具, 这里介绍ALTERA 公司的一款易学易用的CPLD 开发软件MaxPlusII,虽然该公司最新版的软件是QuartusII,但针对某些具体的器件,选择MaxPlusII 还是很方便的。该软件入门教程请到百度搜索《MaxplusII 设计CPLD 入门》,很多手把手的资料。

最容易的电路设计方法不外乎是直接绘制电路原理图。采用原理图输入,初学者甚至不需要额外学习就可以从事CPLD 设计。我们只需要在软件平台上从集成器件库调出对应的器件,绘制相同的电路原理图即可,实现以上功能电路原理图绘制完成后如图6 所示。

图6 原理图输入设计CPLD

该原理图编译成功后,我们还需要根据实际电路连接图分配绑定引脚,引脚绑定如图7 所示,再编译就可以得到可供下载的文件*.pof 了,最后只需要将下载电缆连接到电路板上,仍然通过该软件即可完成下载。

正因为CPLD 的IO 脚是可以随意分配的,通常我们会结合实际的PCB

- 电子电路设计之C51单片机常见问题(10-22)

- C51单片机看门狗电路(02-14)

- 51单片机数字钟温度计的编程实例(05-12)

- 基于FPGA和8051单片机IP核的多功能频率计的设计与实现(02-07)

- 51单片机串口通信原理与应用(02-08)

- 基于51单片机--C语言之预处理总结(07-17)