SOC中多片嵌入式SRAM的DFT实现方法

时间:11-15

来源:本站整理

点击:

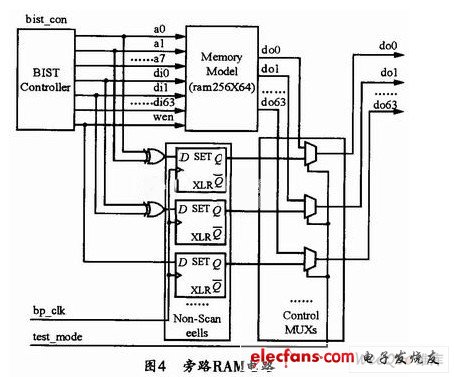

了将故障响应从它的一个输入传播到它的输出,可根据方便程度设置所有其他的输入为0或1。而对于AND/NAND门,为了将系统的故障响应从它的一个输入传播到它的输出,则必须通过将其他输入设置为l来实现,其中"l"对于AND/NAND门是一个非控制值。同理,"0"对于OR/NOR门也是一个非控制值。图4所示是旁路RAM的电路示意图。图中,多路选择器由test_mode信号控制,与RAM的输入输出连接的逻辑可测,RAM模块的测试覆盖率可提高到98.3%,相应的整个芯片的测试覆盖率提高了4个百分点。

由此可见,MBIST结构可直接实例化地用在数字设计部分。该系统的功能逻辑部分含有万余寄存器,为了提高测试覆盖率添,加几个寄存器及很少组合逻辑作为测试点后,即可将测试覆盖率提高且不会增加太大的面积开销,因而这种方法是很有效率的。如果前期设计时就能考虑这种测试结构,DFT设计过程中就会减少反复,减少测试设计周期。

5 结束语

本文基于一个实际项目,分别用常用的并行与串行两种方式来实现MBIST的构架,并对其开销进行了定量与定性讨论,结果是对于不同的设计,应当灵活构建测试结构以达到设计目的。对于在嵌入式存储器数量较少,位宽较小的情况下,MBIST对扫描测试覆盖率的影响并不明显,易被人们忽视,一旦这种影响显著发生,比较高效的方法是插入旁路电路,这样,在提高覆盖率的同时也不会增加太大的面积开销。可见,对于一个嵌入多片SRAM的SOC进行DFT设计时。应从多维度灵活处理,折中考虑。

- 提高智能电表精度新方法,内置高耐度nvSRAM(02-24)

- SRAM特点及工作原理(07-02)

- SRAM模块,SRAM模块结构原理是什么?(02-24)

- 非易失性SRAM DS1747(08-28)

- 基于SRAM的FPGA设计IP的解决方案(03-07)

- 基于Microsemi FPGA的TFT控制的四大解决方案(04-07)