SRAM模块,SRAM模块结构原理是什么?

SRAM模块,SRAM模块结构原理是什么?

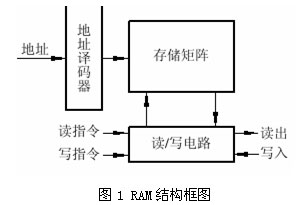

RAM 结构框图如图1 所示。它主要由存储矩阵(又称存储体)、地址译码器和读/写电路 3 部分组成。存储矩阵是存储器的主体,其他两部分称为存储器的外围电路。

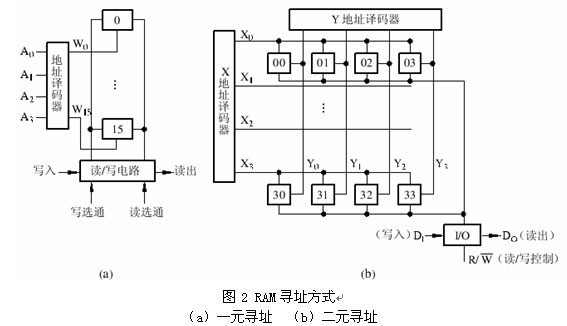

存储矩阵是由许多存储单元有规则地排列构成的,每一个存储单元可以存储一位二进制码。对每个存储单元用二进制码编号,即构成存储单元的地址,为了选中给定单元的地址,可以采用一元寻址(又称为字结构或单译码结构),或者二元寻址(又称位结构或双译码结构)。其逻辑框图如2 所示,图中,存储矩阵包含 16 个存储单元,所以,需要 16 个地址。图2(a)是一元寻址,由 4 位地址码便可构成 16 个地址,即 16 条字线,每条字线为 1 电平时便选中相应存储单元。被选中单元通过数据线与读/写电路连接,便可实现对该单元的读出或写入。

图 2(b)为二元寻址逻辑图,它有 X 和 Y 两个地址译码器。每个存储单元由 X字线和 Y 字线控制,只有在 X 和 Y 字线都被选中时才能对该单元读出或写入。二元寻址可以大大减少字线数量。所以,在大容量 RAM 中均采用二元寻址。

静态 MOS 存储单元

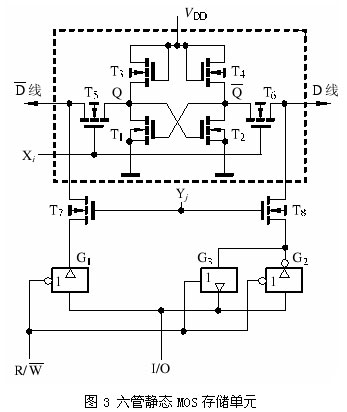

图 3 所示的是静态 MOS 六管存储单元。图中,X i和 Yj为字线;I/O 为数据入/输出端;R/ W 为读/写控制端。当 R/ W =0 时,进行写入操作;当 R/ W =1 时,行读出操作。

电路均由增强型 NMOS 管构成,T1、T3和 T2、T4两个反相器交叉耦合构成触器。电路采用二元寻址,当字线 Xi和 Yj均为高电平时,T5~T8均导通,则该单元选中,若此时R/ W为1,则电路为读出态,三态门G1、G2被禁止,三态门G3工作,存储数据经数据线 D,通过三态门 G3至 I/O 引脚输出。若 R/ W 为 0,则三态G1、G2工作,三态门 G3被禁止,由 I/O 输入数据经 G1、G2便写入存储单元。

静态MOS-RAM(简称 SRAM)

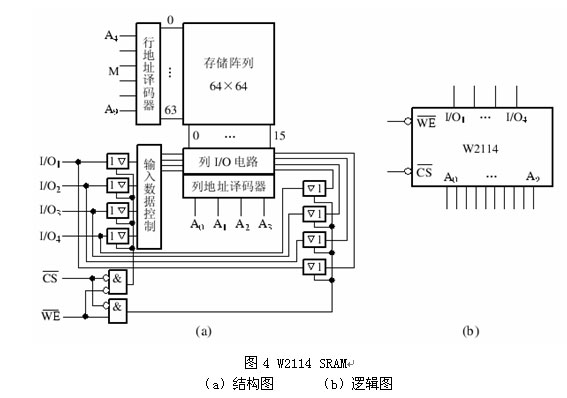

SRAM产品种类繁多,在容量与功耗等指标上有很宽的覆盖面,可供不同的场合应用,但基本电路结构大同小异。图4是W2114 SRAM(1K*4位),这是一种典型结构,5H2112(256*4)和美国的HM6116(2K*8)位都是采用这种结构。它采用HC-MOS工艺(H表示高速),所以,具有高速、低耗、单一5V电源、外围电路简单、输入输出引脚公用、三态输出、使用非常简单以及存取时间短(为100ns)的特点。

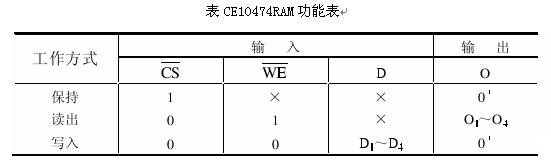

CS为选通端, WE 为写使能控制端,A0~A9为地址,I/O1~I/O4为输入/输出。显然可见为二元寻址和三态输出结构。 CS为低电平有效,电路选通之后,若要写入操作,则令 WE =0,输入三态门被选通(高电平有效),数据通过输入控制电路被写入;与此同时,输出三态门关闭,切断了输出与数据总线的联系。若要读出,则令 WE =1,输入三态门关闭而输出三态门被选通,因而存储数据被读出。功能表示于下表。

SRAM 相关文章:

- 提高智能电表精度新方法,内置高耐度nvSRAM(02-24)

- SRAM特点及工作原理(07-02)

- 非易失性SRAM DS1747(08-28)

- 基于SRAM的FPGA设计IP的解决方案(03-07)

- 基于Microsemi FPGA的TFT控制的四大解决方案(04-07)

- 串行和并行接口SRAM对比,谁会是未来主流?(10-06)