可复用SPI模块IP核的设计与验证

2.2 SPI模块功能设计

根据功能定义及SPI的工作原理,将整个IP分为8个子模块:APB接口模块、时钟分频模块、发送数据FIFO模块、接收数据FIFO模块、状态机模块、发送数据逻辑模块、接收数据逻辑模块以及中断形成模块。

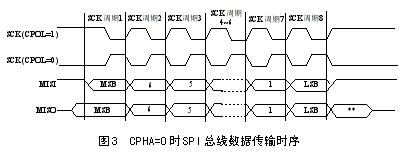

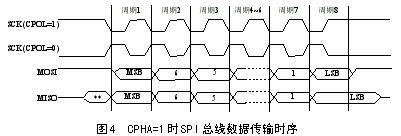

深入分析SPI的四种传输协议可以发现,根据一种协议,只要对串行同步时钟进行转换,就能得到其余的三种协议。为了简化设计规定,如果要连续传输多个数据,在两个数据传输之间插入一个串行时钟的空闲等待,这样状态机只需两种状态(空闲和工作)就能正常工作。相比其它设计,在基本不降低性能的前提下,思路比较精炼、清晰。

此SPI模块有两种工作方式:查询方式和DMA方式。查询方式通过处理器核监视SPI的状态寄存器来获知其所处的状态,从而决定下一步动作。DMA方式由DMA模块控制数据在内存和SPI间的交换,而不需要处理器核的参与,有效提高了总线利用率。

3 EDA软件仿真与FPGA验证

为了保证设计的鲁棒性,运用多种方法对此IP的功能进行了全面的仿真和验证。

首先进行EDA软件仿真验证。这种仿真包括RTL级和门级仿真验证。RTL级仿真只是将代码文件调入硬件描述语言的仿真软件进行功能仿真,检查逻辑功能是否正确。门级仿真包括布局布线前和布局布线后仿真。布局布线后仿真,可以获得比较精确的时延参数,能够比较真实地反映芯片制造完成后,模块在实际工作中的行为与性能,所以通过了此类仿真就认为模块设计成功,可以进行流片。将RTL级代码转换成门级网表,使用的是Synopsys公司的综合工具DC(Design($9.9900) Compiler)以及台湾集成电路制造公司(TSMC)的0.25μm标准单元库。

在传统的设计流程中进行功能验证,首先需要通过写测试矢量的方式给需要进行功能测试的模块加激励,然后通过观察模块的输出结果,判断模块的功能是否正确。但是在写测试矢量时,测试工程师是在自己对模块功能理解的基础上进行的。这样就存在一个问题,测试矢量对模块的激励有可能是不完备的,还有可能是错误的。由此有可能模块的功能是错误的,但测试矢量的激励并没有使错误体现出来;也有可能模块的功能是正确的,误报错误使验证过程变得非常低效[5]。为避免以上问题,在模块的功能验证中,采用系统级验证环境。该环境由IP 总线、驱动器、监视器、外部模块和协调它们工作的脚本组成。组成系统的各模块可以按需要加入环境。每次验证过程就是相应的激励作用于环境的过程。验证结果由环境产生、检验和输出。该验证环境在SOLARIS5.8操作系统下,仿真器采用Synopsys公司的VCS,支持C/C++、Verilog和VHDL协同仿真,可以直接将SPI模块挂在验证环境中,通过Verilog的$readmemh任务读入软件激励进行验证。

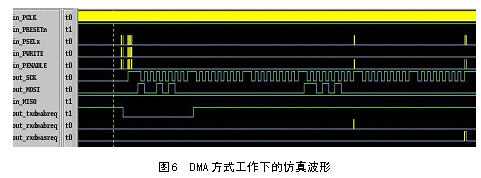

在系统时钟为66MHz,CPOL=1、CPHA=0下收发6字节数据的仿真结果如图5、6所示。

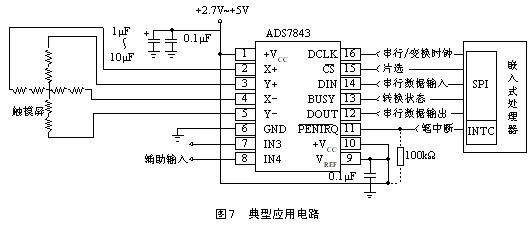

SPI模块的典型应用是:通过与带SPI接口的触摸屏控制芯片连接,提供对触摸屏的支持。针对此目标,将SPI模块及其它必要模块加载到FPGA中进行硬件、软件联合调试,对实际电路进行验证。我们选用了最常见的四线式电阻式触摸屏,而触摸屏控制芯片采用ADS7843($1.8886)。ADS7843($1.8886)是一个内置12位模数转换、低导通电阻模拟开关的串行接口芯片,支持8和12位的A/D转换精度。为了完成一次电极电压切换和A/D转换,微处理器需要先通过SPI接口往ADS7843($1.8886)发送控制字,转换完成后再通过SPI接口读出电压转换值。标准的一次转换需要24个时钟周期[6]。典型的应用电路如图7所示。

SPI的FPGA验证平台包括ARM公司提供的Intergrator/LM-EP20K1000E和Intergrator/CM7TDMI开发验证板以及Garfield II验证电路板(自行设计)。其中Intergrator/CM7TDMI上的ARM7TDMI微处理器内核作为整个开发系统的CPU。通过ARM Multi-ICE,将验证必需的包括SPI在内的所有模块由JTAG口加载到Intergrator/LM-EP20K1000E板上Altera APEX20KE系列的EP20K1000EFC672中。外围电路由Garfield II验证电路板(包含ADS7843($1.8886))以及触摸屏组成。在FPGA上通过软硬件协同验证,通过逻辑分析仪观测SPI总线信号,也证明此SPI模块性能良好。

另外,通过台湾集成电路制造公司(TSMC),采用其0.25μm标准单元库对该设计多次进行流水验证,获得的实际IP电路在样机中工作十分稳定。至此,IP的设计十分成功。当设计相似架构的SoC芯片时,可根据需要配置相应参数后直接进行复用。

结 语

建立经过充分验证的功能正确、性能良好的可复用IP模块库,是快速进行SoC设计的基础和要求。设计可复用的IP,需要遵守一定的设计方法:完整、清晰的文档;良好的代码风格;详细的注释;精心设计的校验环境;极高代码覆盖率的测试向量等。本文以SPI模块IP为例,按照规范的流程和要求,进行了初步的尝试,得到了较好的结果。

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于FPGA的8段数码管动态显示IP核设计(02-03)

- 基于FPGA和IP Core的定制缓冲管理的实现(08-14)

- 基于Altera ASI IP核的ASI发送卡实现(02-25)

- FPGA的高速多通道数据采集控制器IP核设计(04-22)

- 基于EDA或FPGA的IP保护的实现(09-16)