基于DE2的开源片上系统Freedom E310移植

ilog HDL代码,然后才可以综合。

2 启动过程分析及bootrom设计

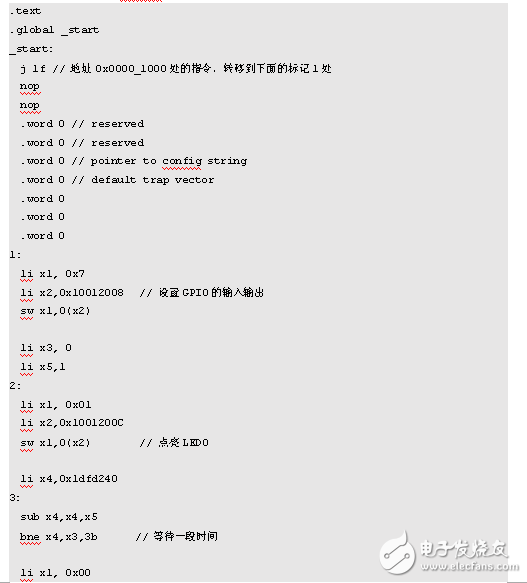

Freedom E310是可配置的SoC,可配置ROM、OTP、QSPI,依据其配置情况,有不同的启动过程,默认的启动过程是,从ROM处(0x0000_1000)开始执行,ROM处一般存储一条转移指令,转移到OTP,或者QSPI。Altera的DE2开发平台没有QSPI接口的flash,所以只能转移到OTP,为了进一步简化移植验证难度,本文并不使用OTP,而是在0x0000_1000处存储了一条转移指令,该转移指令转移到ROM中的另一处地址继续执行。ROM中的代码就是bootrom,其主要内容如下。

上述bootrom的代码在启动后转移到标记1处,开始配置GPIO,使其GPIO0为输出口,然后通过该接口送出一个高电平,等待一段时间后,在送出一个低电平,循环执行该过程。如果GPIO0连接到LED,将会发现该LED不停的点亮、熄灭。

3 基于DE2的开源片上系统Freedom E310移植

3.1 实验环境

本文的实验平台是Ubuntu14.04,在Github上clone下列项目的代码:Rocket-chip、Freedom、Freedom-e-sdk。编译Rocket_chip的代码,得到对应的GCC工具。

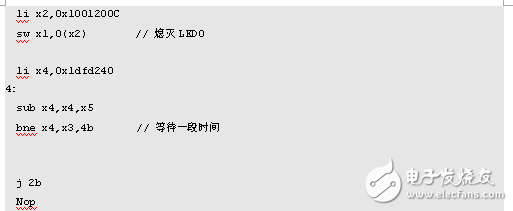

3.2 编译bootrom

3.3 生成Freedom E310对应的Verilog HDL文件

使用如下语句可以编译得到Freedom E310对应的Verilog HDL文件。

make -f Makefile.e300artydevkit verilog

生成的Verilog HDL文件位于builds/e300artydevkit/路径下,文件名是sifive.freedom.everywhere.e300artydevkit.E300ArtyDevKitConfig.v,并且其ROM的内容就是bootrom.img的内容。

3.4 建立QuartusII工程

建立QuartusII工程,添加如下文件到该工程,其中system是顶层模块。

freedom\fpga\e300artydevkit\src\system.v

freedom\sifive-blocks\vsrc\SRLatch.v

freedom\rocket-chip\vsrc\AsyncResetReg.v

freedom\rocket-chip\vsrc\DebugTransportModuleJtag.v

Freedom\builds\e300artydevkit\sifive.freedom.everywhere.e300artydevkit.E300ArtyDevKitConfig.v

3.5 修改system.v

System是顶层模块,其中例化了Freedom E310,但是system中使用了许多Xilinx平台的IP,需要进行针对Altera平台的修改。

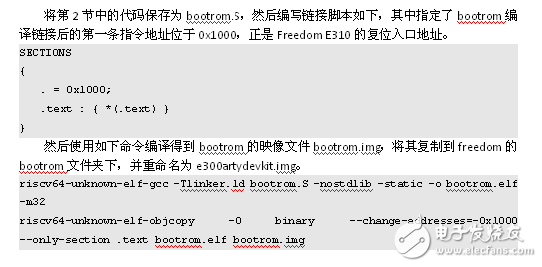

3.5.1 修改mmcm

3.5.2 修改sys_reset

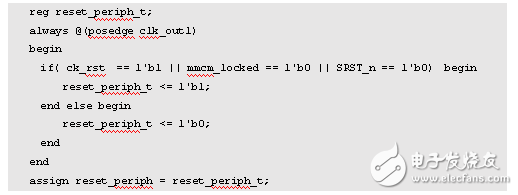

sys_reset模块使用的是Xilinx的proc_sys_reset IP,其作用是生成复位信号,可以使用下列代码代替。

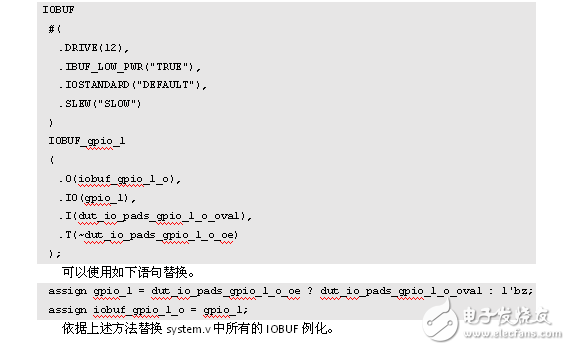

3.5.3 修改IOBUF

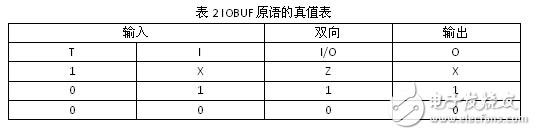

system.v中使用了大量的Xilinx IOBUF原语,IOBUF是单端双向缓冲器,由IBUF、OBUFT两个基本组件组成,当I/O端口为高阻时,其输出端口O为不定态,其输入输出真值表如表2所示。

依据上述真值表,假设有如下IOBUF例化。

依据上述方法替换system.v中所有的IOBUF例化。

3.6 引脚设定

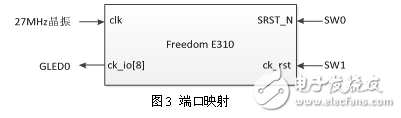

参考bootrom的功能,本文使用到了复位、时钟、GPIO0、SRST_N等几个端口,其在DE2平台的映射如图3所示。

3.7 编译下载

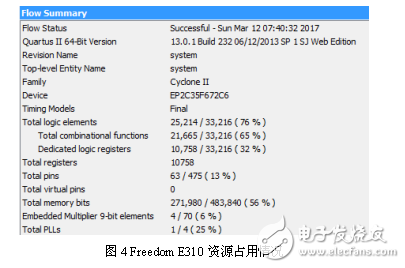

经过上述修改后,在QuartusII中编译下载,保持SW0为高电平输入,SW1为低电平输出,就可以观察到GLED0灯不停的点亮、熄灭。说明Freedom E310运行正常。资源占用情况如图4所示。

结语

Freedom E310是第一款基于RISC-V指令集架构的开源商业SoC,具有丰富的外设,满足多种应用场景,并且具有可配置的特性,适合根据应用进行裁剪,本文给出了将Freedom E310移植到Altera DE2开发平台的步骤,对于其他计划使用Freedom E310的用户具有一定的借鉴意义。

参考文献

[1]Waterman, A. et al. The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1[S], 2016

[2]SiFive, Inc. SiFive E3 Coreplex Series Manual, Version1.2[S], 2016

[3]SiFive, Inc. SiFive FE310-G000 Manual, Version1.0.1[S], 2016

[4]Chisel 2.2 Tutorial[EB/OL]。 https://chisel.eecs.berkeley.edu/2.2.0/chisel-tutorial. 2016-10

作者简介:

雷思磊:通信公司工程师,研究方向为处理器架构,嵌入式处理器应用等

freedom系列 coreplex 半导体芯片 soc 相关文章:

- 大咖谈数字音频解决方案,百年电声华人第一次(04-23)

- 掌控时局,看芯片商如何争夺汽车互联市场!(05-02)

- 从1.0到3.0,Hi-Fi颠覆了智能手机行业!(05-21)

- 一位台湾工程师透露,大陆从台湾挖高端IC人才很疯狂(02-23)

- USB Type-C芯片稀缺时代将成过去时(09-12)

- 国产“安防芯”腾空出世 凸显“芯”地位(02-11)