通过路径发现优化IC-Package-PCB

规模越来越大的芯片级集成(包括多芯片封装和三维)以及对不断缩小产品外形参数的要求,让超高管脚数目器件的扇出和布线变得异常困难。此外,跟踪所有信号和管脚也是采用现有方法无法解决的一大难题。由于高管脚数目器件具有成本敏感性这一特点,工程师们不得不重新考虑在对复杂的 IC 封装变量进行折衷的同时,如何规划和优化芯片的 I/O 布局,并且针对多个板级平台(外形参数)进行所有这些工作。

大多数公司都使用 Microsoft® Excel® 作为跟踪信号和管脚的工具。这些非正式流程旨在将多个 EDA 设计工具集成到一起。这样的做法毋庸置疑。然而,如果没有中心数据存储库或精确的器件建模和基于规则的优化运作,设计意图往往就会被曲解或遗忘,而且往往会将设计冗余引入流程中。

需要开发正式的协同设计流程来集成诸多关键功能。这一流程可在引入多个潜在板级平台概念的同时满足 IC、封装基底以及印刷电路板设计师的相关要求。本文旨在确定并讨论在整个IC-Package-PCB 设计流程中用于优化管脚/封装选择的方法。

适用于不同终端产品的不同封装方法

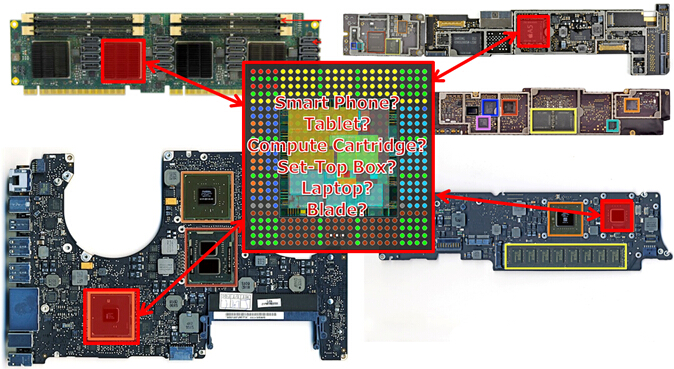

对于很多产品来说,多个产品系统会使用相同的芯片集。例如,一个处理器可能会同时针对智能手机和平板电脑的外形参数。每个平台都可能拥有独特的机械、热学和电气要求。因此,为每个平台确定最具成本效益的封装方法可谓一项巨大的设计挑战。

图 1:相同的芯片集可能用于多种外形参数的产品中。这可能需要为不同的产品使用不同的封装方法,以便于其在物理约束中工作。

如果处理器需要与多个供应商提供的内存器件配合使用,而每台内存器件都拥有自己的管脚,那该怎么办?在这种情况下,为处理器封装确定理想的管脚应与板级布线研究相结合。那么根据特定要求为使用同一IC的最终用户提供多种封装选择怎么样?如果稍微调整一下您封装上的管脚间距可以增加可布线 PCB 的数量,从而减少布线层的总数量,情况又会怎样?

这些任务以及类似封装路径发现的其他任务主要通过 Microsoft 工具和白板讨论的方式执行,这类很不正式的设计流程很少能够提供设计自动化,因此不但容易出现人为错误,而且还可能导致大量的设计冗余。

为帮助实现自动化流程,一些公司围绕 Excel 创建了封装管脚(球输出)解决方案。这种采用规划和优化当前球栅阵列 (BGA) 的管脚的方法已经过时,涉及的因素很多,包括:

· 跨域协同设计所能提供的支持有限

· 扇出和迂回布线可视化

· 互连可视化(飞线)

· 拆解/理清互连

· 基于规则的管脚分配

· 不规则间距 BGA 的所见即所得表示

· 与布局和分析工具的集成较弱

· 动态管脚调整

· 原理图符号的自动生成

图 2:典型的内部 Excel 电子表格球输出示例。

理想的IC-Package-PCB设计流程

跨域互连规划和优化对于确定最佳封装和管脚至关重要。我们需要一个集成平台,这一平台可以对 IC 底层规划和 I/O 要求进行建模,并纳入封装基底约束和变量以及多个 PCB 平台(外形参数)。应根据不同领域充分利用行业标准。例如,适用于 IC 数据和 Excel 的 LEF/DEF 或适用于封装基底数据 AIF。这一方法能够让工程师实现整个系统的可视化。

一旦系统被捕获,全面连通性管理系统可以补偿跨域信号命名冲突和电源/接地短路。该连通性管理系统应支持每个设计团队所熟悉的使用模型。例如,适用于芯片设计师的 HDL 和适用于电路版设计师的原理图。

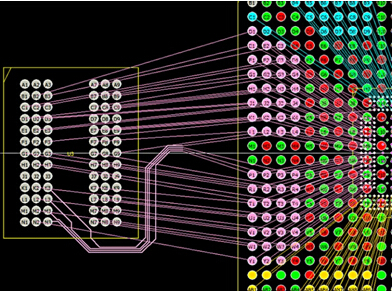

封装管脚在优化流程中的灵活性最高。然而,并不是封装上的每个管脚都可采用相同的方法处理。诸如差分对需要集成在一起以及必须考虑信号功率比等因素。因此,规则引擎应用于控制/指导管脚优化算法。而仅仅优化管脚间的互连已远远不够。管脚的优化必须同时考虑由封装基底设计师以及电路板布局设计师执行的任何迂回和扇出布线的情况。

图 3:采用优化后IC-Package-PCB管脚进行的完整扇出示例。

能够在尝试确定最佳封装及其管脚的同时对多个平台进行评估尤为重要。最佳解决方案就是使用一个能在单个项目中支持多个设计和情境的集成平台。最后,库的自动化功能不容小觑。只有在原理图符号存在的情况下,电路板设计师才能使用最终生产 PCB 上的器件。BGA 管脚优化后,器件从本质上便已为库生成做好准备。

自动化这一流程不仅可以加速进程,还可以消除人为错误。符号的生成必须考虑基于许多要求的多种分散因素,例如原理图图纸尺寸和端口/信号分组等。此

- 如何解决汽车制造商多样性价值和复杂性成本的矛盾?(06-18)

- 新一代的系统设计,让封装和PCB设计更简单(02-19)

- 芯片设计完成,如何确认功能达到100%(08-28)

- PCB布线技术中的抗干扰设计(03-08)

- 基于Protel 99 SE环境下PCB设计规范与技巧的研究(08-30)