借用同步整流架构提高电源转换器效率

随着消费性电子的发展,各种供电电源如适配器所消耗的电能占全球能耗的比例急剧加大,成为不可忽视的耗能「大户」。以美国为例,每年适配器须要消耗电能3,000亿度,占整个国家每年用电总量的11%。

现今节能减碳声浪不断提高,各国政府法规对电源的要求也越来越严格。美国能源部(Department of Energy, DoE)针对External Power Supply公告新的要求NOPR(Notice of Proposed Rulemaking),将对电源供应厂与相关节能零件带来新的挑战,表1为针对效率的要求。详细资料可参考美国能源部官方网站。

同步整流晶片加速取代二极管

手持式电子产品如平板装置(Tablet Device)、智慧型手机等的风行,相对地亦开始要求电源充电器的尺寸必需短小轻薄,这些因素也对电源设计造成新的挑战。

近年来电子技术的发展,使得电路的工作电压越来越低、电流越来越大。低电压工作有利于降低电路的整体功率消耗,但也给电源设计提出新的难题。

开关电源的损耗主要由三部分组成,分别为功率开关元件、变压器及输出端整流管的损耗。在低电压、大电流输出的情况下,整流二极体的导通压降较高,输出端整流管的损耗尤为突出。快恢復二极体(FRD)或超快恢復二极体(SRD)可达1.0或1.2伏特(V),即使採用低压降的萧特基二极体(SBD),也会产生大约0.5~0.6伏特的压降,这就导致整流损耗增大、电源效率降低。整流管上的损耗也会达到电源总损耗的60%以上。

因此,传统的二极体整流电路已无法满足实现低电压、大电流开关电源高效率及小体积的需要,成为制约交流对直流(AC-DC)电源供应器提高效率的瓶颈。为能有效降低功耗及温升,近来使用同步整流技术以取代整流二极管蔚为风潮。

同步整流是採用通态电阻极低的专用功率金属氧化物半导体场效电晶体(MOSFET),来取代整流二极体以降低整流损耗的一项新技术,它能提高开关电源供应器的效率。MOSFET属于电压控制型元件,它在导通时的伏安特性呈线性关係。以功率MOSFET做整流器时,要求闸极电压必须与被整流电压的相位保持同步才能完成整流功能,故称之为同步整流。

晶片商竞推同步整流晶片

MOSFET耗损主要由内阻(Rdson)决定(切换速度《200kHz),萧特基二极体耗损则由顺向压降(Vf)来决定。当多颗MOSFET并联时内阻会成倍数下降,理论上并联无数颗MOSFET时,内阻会趋近于零几乎没有耗损。但萧特基二极体物理上存在最低屏蔽顺向压降约0.3伏特,不论并联多少颗萧特基二极体,最低都有此屏蔽压降,因此最低也会约有耗损Ploss=0.3×输出电流。

基本单端自激、隔离式降压同步整流电路如图1所示。V1及V2为功率MOSFET,在次级电压的正半周,V1导通,V2关断,V1起整流作用;在次级电压的负半周,V1关断,V2导通,V2起到续流作用。同步整流电路功率耗损包括V1及V2导通损耗及闸极驱动损耗。当开关频率低于200kHz时,导通耗损占主导地位。

图1 单端降压式同步整流器的基本塬理图

自激式的同步整流架构很简单,但是为能确保在使用时不发生失控电路烧毁或不稳定情形,周边须加入保护电路,因此近年来各厂商陆续推出二次侧同步整流控制IC。

ZCD和预测式同步整流技术分庭抗礼

自90年代末期同步整流技术诞生以来,开关电源技术得到极大的发展,採用IC控制技术的同步整流方案已为研发工程师普遍接受,现在的同步整流技术分为两大类,分别为零电流侦测(ZCD)及预测式(Prediction)的同步整流方案。

不论使用何种方案,效率的提升主要决定于MOSFET的选择,由于开关电源供应器的使用频率,通常是在200kHz以下,因而MOSFET的内阻决定大部分的效率的提升。

ZCD有恩智浦(NXP)、国际整流器(IR)和安森美(ON Semiconductor)等厂家投入,预测式则是擎力科技的专利。这两种方案各有优点,ZCD的周边零件较少、调整较易、适用于非连续导通模式 (DCM);而预测式的优点是可同时使用于DCM及连续导通模式(CCM)之间、不挑选MOSFET和死区(Dead Time)可调整。

所谓ZCD就是当侦测到MOSFET汲极的电流为零时,IC输出一个高位準给MOSFET,由于是侦测电流,因而MOSFET的内阻变化会影响到电流,为了操作安全,各厂商均设定在-200?300毫伏特(mV)才做切换(图2)。

图2 ZCD电流侦测图示

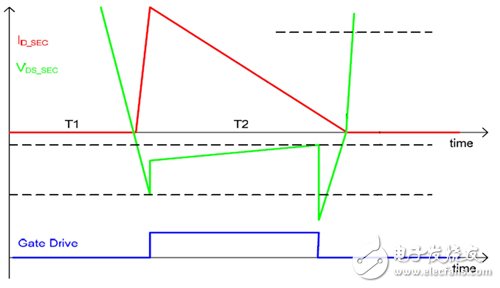

预测式是利用上一波形来预测下一波形,因此可以在MOSFET的Vds电压上升之前,提前截止Vgs,以避免MOSFET的交越。

图3和图4分别为工作在CCM、DCM下的同步工作波形,其中上方波形为同步MOS的Vds波形,下方波形为SP6018输出波形。

- 基于同步整流技术的反激变换器(09-14)

- 如何让同步整流器达到高效率标准(10-16)

- 60A交错式有源钳位正向转换器设计(03-09)

- 详解同步整流技术在正激变换器中的应用(07-08)

- 隔离型μModule电源转换器 改善了信号测量准确度 可在严苛的电气与热环境中工作(03-05)

- 如何廉价地制作了110伏至12伏的电源转换器(06-28)