28nm高端FPGA如何实现功耗和性能的平衡?

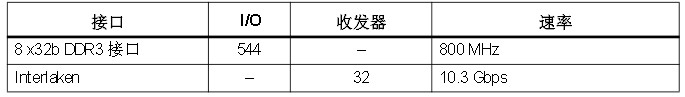

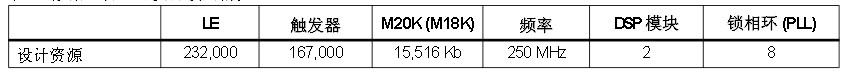

况,表5提供了I/O和收发器数据,表6提供了输入到XPE (14.2)和 EPE (12.0 SP2)中的信息。

表5 数据流管理器I/O和收发器信息

表6 数据流管理器资源使用情况

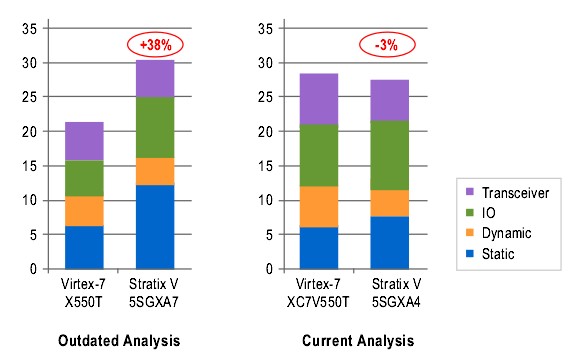

图5对比了获得的新L器件结果和以前报告的结果,再次表明,与Virtex-7 FPGA相比,Stratix V FPGA降低了功耗,同时提高了性能。

图5 使用L器件,更新后的数据流管理器功耗对比

这个例子显示了3%的功耗优势,100GbE OTU4转发器实例显示了8%的功耗优势,还有客户设计表明有15%的功耗优势。Stratix V器件还具有1个速率等级性能优势。

双 100G转发器实例

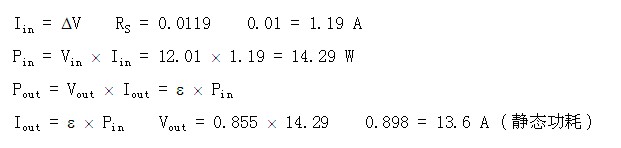

EPE的精度如何?或者换句话说,上面对比的结果有多可靠?第三个例子对比了测量值和EPE估算值。正如前面所提到的,最终功耗估算的次优方法获得了正确的输入触发率,在无矢量模式中使用了PowerPlay功耗分析器。这一方法是用于开发以下Altera100G双转发器设计的方法。对于这一设计,按照引脚连接指南中的建议,将VCC、VCCHIP和VCCHSSI连接起来。设计电路板时,使用0.9 V ES器件,在供电通路(12.01 V)上采用0.01 1%电阻连接电压稳压器。运行时,电路板处理OTN数据流几个小时,达到稳定工作温度后,进行以下测量:

Ÿ 稳压器输入电压:12.01 V

Ÿ 稳压器输出电压:0.989 V

Ÿ 电阻上的压降:1.19 A

然后,器件停止工作(所有时钟都停止),进行另一次测量,获得同一结温时设置的器件泄漏电流,作为总电流。测量的电阻压降是11.9 mV。使用了下面的计算:

稳压器效率基于数据图表,外推为 0.9 V。

0.9V电源上的动态电流(I cc+ Icchssi + Icchip) = 22.7 – 13.6 = 9.1 A

PCIE引脚由PCB供电,但是并没有在内核中例化HIP。

从 Quartus II软件导入CSV文件后,从12.0 SP2 EPE中得到相应的结果是10.1 A的总动态电流。

最终结果是,使用来自Quartus II软件的无矢量分析CSV文件,EPE比测量值9.1 A高出1 A(11%)。对于早期功耗估算,这一分析结果非常精确。

结论

在客户设计中,从器件体系结构定义中关注功耗和性能的均衡,以尽可能低的功耗实现最佳性能和带宽,与其他28 nm产品相比,降低了功耗。通过Stratix V FPGA以下的功能,设计人员实现的系统具有明显的优势:

Ÿ Altera定制的TSMC 的28HP工艺

Ÿ 低电压(0.85 V)体系结构

Ÿ 功能模块的硬关断

Ÿ 大量的硬核IP

Ÿ 可编程功耗技术

Ÿ 宽带高功效收发器

Ÿ I/O创新实现了高功效存储器接口

Ÿ Quartus II软件功耗优化

Ÿ 逻辑和RAM时钟选通

Ÿ 使用方便的部分重新配置功能

28nm Altera Stratix 收发器 FPGA 相关文章:

- CEVA携Sensory力推先进的语音识别解决方案(02-12)

- 通过应用案例告诉你:赛灵思如何做到领先一代(02-12)

- 传统过孔数显著增加 条状过孔成大势所趋(08-02)

- Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex(02-11)

- 基于DSP和FPGA的机器视觉系统设计与实现(03-07)

- Altera在OFC 2014上推出400G以上OTN解决方案(02-12)