28nm高端FPGA如何实现功耗和性能的平衡?

和性能。以太高的功耗满足性能要求,或者功耗较低但是没有达到性能目标,这都是不可使用的设计。因此,Quartus II软件还必须能够在性能和功耗上很好地达到均衡。在没有用户干预的情况下,工具会自动只在需要的地方使用高速块,尽可能降低功耗泄漏以满足性能要求,同时使得所有其他块进入低功耗状态以减小泄漏。此外,还采取了以下降低功耗的措施:

Ÿ 逻辑、RAM 分析、重新规划,以降低动态功耗

Ÿ 群布局减小了走线长度,降低了动态布线功耗

Ÿ 优化布局以减小时钟功耗以及非关键通路信号布线功耗

建模是重要的步骤,因为它保证了功耗模型的正确性,不是最差也不是最乐观。公司可以选择保守、激进或者正确的方式。最终,最适合设计人员的唯一选项是正确地建模。保守选择导致了估算的功耗在市场上看起来并不具有竞争优势。激进的选择导致最终功耗与工具估算的功耗不具有可比性。做到正确的选择尽可能接近硅片实际测量的功耗,同时满足了供应商和客户的要求。

在制造过程中降低功耗,提高性能

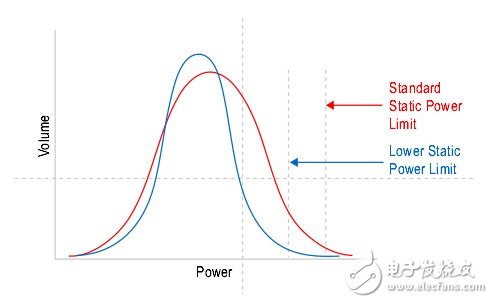

提高制造能力,大批量交付器件是提高产量、严格工艺的关键。Altera早期以标准功耗指标发售器件,以帮助前沿的客户满足早期原型开发和生产进度要求,然后,严格曲线指标,尽快实现利益,以帮助这些用户满足其产品进度和功效目标。Altera采用这一严格的工艺来交付低静态功耗的新L(低功耗)器件。

如图3示,减小工艺变化使得静态功耗降低了35%,从而降低了总功耗。由于结温增大和漏电增加是一种指数函数关系,因此,这一方法在较高结温时极大地降低了功耗,满足了当今很多系统设计的要求。

图3 工艺降低了静态功耗

在28HP制造工艺降低功耗的结果非常显著,因此,Altera立即将其应用于独具优势的FPGA上,在产品代码中标以"L"。这种突出显示的订购码旨在将产品立即应用于对功耗敏感的设计中,然后,在所有28 nm产品中继续发挥同样的工艺优势。

在FPGA 设计中使功耗和性能达到均衡

设计人员能够使用高端器件,当这些工具具备了各种低功耗功能以及支持功耗预知的情况下,设计人员自己会确定怎样均衡其每一设计的性能和功耗。他们从选择正确的FPGA系列开始。当需要最佳性能或者最大容量时,选用Stratix V FPGA。在Stratix V系列中,可用的型号包括没有收发器的器件、有收发器的器件,以及重点是DSP应用的器件。

选择好器件后,在FPGA设计过程中,可以使用几种设计方法来降低功耗,包括,逻辑和RAM时钟通道以及部分重新配置等。

即使采用了最佳设计方法、模型和软件,也只有提供了输入后才能进行功耗估算。大部分设计人员熟悉基本动态功耗方程:CV2F X (触发率)。设计工具计算电容(C),已知电压(V)和频率(F)是已知的,但是不知道设计的触发率。确定触发率的最佳方法是运行代表实际系统使用情况的仿真,得到.vcd文件后,使用PowerPlay功耗分析器工具。次优的方法是为I/O建立合适的触发率,根据得到的估算,使用 PowerPlay功耗分析器来产生内部触发率。第三好的方法是使用早期功耗估算器 (EPE),使用以前相似设计的触发率。最不精确的方法是以默认触发率使用EPE。功耗估算的精度与默认触发率和设计实际触发率之间的差值相关。 Altera建议使用 PowerPlay功耗分析器,通过矢量获得最佳功耗估算。

设计实例

设计过程中一个重要的早期步骤是,为Stratix V FPGA下载最新的EPE,选择器件 (功耗指标最低的L器件),为设计输入信息。与竞争产品相比,Altera的L器件既有动态功耗优势,又具有总功耗和性能优势。

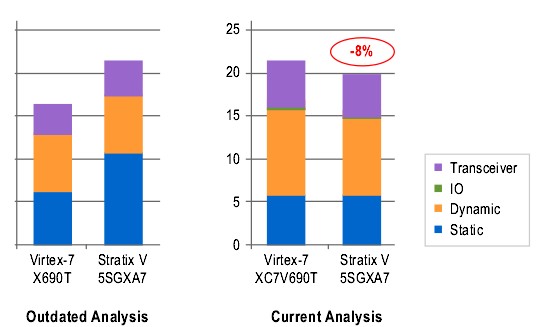

下面的例子包括竞争对手以前分析的两个设计,使用14.2 XPE和Quartus II 12.0SP2 EPE进行了更新,以及一个使用VCC(内核)电源的新例子,针对Altera的双100G转发器设计进行了测量和预测。

100GbE OTU4转发器实例

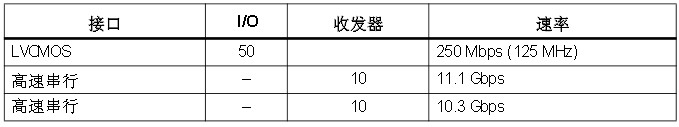

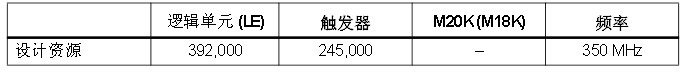

在这个例子中,运行时用户相关的结温是100℃,使用了最大工艺指标。基于竞争对手白皮书中设定的资源使用情况,表3供了I/O和收发器数据,表4提供了输入到XPE (14.2)和 EPE (12.0 SP2)中的信息。

表3 100GbE OTU4 转发器 I/O 和收发器信息

表4 100GbE OTU4转发器资源使用情况

图4对比了获得的新L器件结果和以前报告的结果,表明,与Virtex-7 FPGA相比,Stratix V FPGA降低了功耗,同时提高了性能。

图4 使用L器件,更新后的100GbE OTU4转发器功耗对比

数据流管理实例

在这个例子中,运行时用户相关的结温是100℃,使用了最大工艺指标。基于竞争对手白皮书中设定的资源使用情

28nm Altera Stratix 收发器 FPGA 相关文章:

- CEVA携Sensory力推先进的语音识别解决方案(02-12)

- 通过应用案例告诉你:赛灵思如何做到领先一代(02-12)

- 传统过孔数显著增加 条状过孔成大势所趋(08-02)

- Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex(02-11)

- 基于DSP和FPGA的机器视觉系统设计与实现(03-07)

- Altera在OFC 2014上推出400G以上OTN解决方案(02-12)