面向新一代多核器件的电源管理技术

摘要

现代高频器件所消耗的电量大约有一半是静态电量-漏电与频率无关,但与电压水平相关,另一半则是动态电量-基于系统负载,从而与频率相关。由于频率与电压水平密切相关,因此需要较高的电压水平来驱动频率;一般的概念是利用 DVFS-动态电压和频率调节。也就是说,当系统负载较低时,频率被降低,从而可降低电压。然而,这种方法只能节省一定的电量,对负载变化的反应速度较慢,因此也需要更复杂的系统/板卡解决方案,以不断适应功率和频率。

片上系统尤其是多核器件的优势在于能够完全打开和关闭器件的组成部件,以匹配系统负载。由于在器件内部便可完成上述操作,因此不需要如此复杂的外部电路。然而,在器件内打开和关闭部件过去是一个缓慢的过程,因此不可行,现在这种情况正在发生改变。

通过新一代高端多核器件,飞思卡尔推出了 SRPG(状态保持电源门控)概念。这种技术在掉电时不把模块状态存储到外部存储器,而是允许每个触发器保存自己的状态。因此,整个内核、内核子集或其他功能块可即时打开和关闭。 这推出了一个新的非常有效的执行概念,内核只在需要时才运行,然后只在可能需要时执行单元。

本文简要介绍了现代高端电源管理,以及这种技术如何与工艺技术和设备设计相关。然后展示了如何通过利用 SRPG 进一步改进新一代多核器件,以及设备负载水平感知等其他 SoC 技术自动打开和关闭内核。

引言

随着半导体器件变得更加强大,因此可能消耗大量的电力,电源管理已经成为一个越来越重要的主题。与十年前相比,频率的竞赛已经导致事实上的电源上限和通用的高频。此外,多核和集成度的提高产生了功能非常强大的器件,使功耗管理变得至关重要。在手机等手持设备领域也如此,此类设备应在高性能激活状态和低功耗的待机状态之间进行切换。但在服务器中心也如此,在服务器中心每个区域和/或瓦的性能的重要性日益增加。散热和功耗以及空间等成本比单个器件的最大性能更加重要。多核如今已成为现实,在两个中等性能的器件之间分割应用与在高性能器件之间分割的难易程度相当。基本物理通常为两个中等性能的器件比高端器件提供更高的每瓦和每面积汇聚性能,假定应用可正确地在内核/器件之间进行分割。

在这里,我们将展示现代半导体器件的功耗的基本属性,然后介绍了可包含在设备设计中用于降低功耗的被动节电功能,这些都很容易理解,但通常不要求软件具体使用它们。然后,我们将讨论需要软件与硬件合作以充分利用的主动节电功能。最后将介绍飞思卡尔 QorIQ 器件提供的功耗模式以及它们所利用的功能。

电源基础知识

动态功耗的主要公式为: P = C V2 f

其中 P 代表功耗,单位为瓦,C 代表所切换的设备的电容,V 代表电压,f 代表切换频率。如公式所示,功耗随着频率呈线性增长,但与电压呈平方增长。然而,采用特定工艺技术的器件的最大频率取决于电压有多高,信号被驱动的程度。增加电压可允许更高的频率,但同时也会大大增加功耗。这也是停止大多数增加频率的做法的根本原因之一。

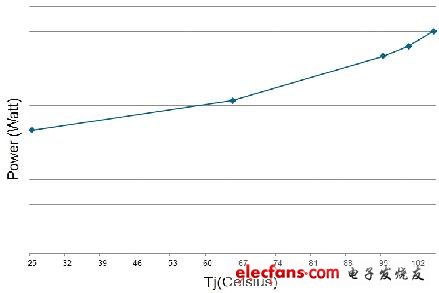

功耗的直接影响是明显发热。虽然功耗本身是有成本的,但主要问题是热效应,因为根据使用情况需要散热片、风扇、空调等冷却设备。而热度增加也影响额定电容,增加功耗。这种相关性是不稳定的,可能导致功率快速增加/热增加,除非热被转移,或功耗降低(通过抑制性能)。重要的是需要了解器件功耗随温度变化有何差异,低结温 Tj 25C 和高结温 105C 之间的差异可能导致功耗显著增加,如图 1 所示。重要的是,如果需要的话板卡电源和热设计可以应对温度升高,但同样重要的是需要了解低温下的功耗将大大低于器件设为最大功率时的功耗。因此,在确保低温的情况下使用器件可降低功耗。例如,许多环保标准允许缩减功能,即如果环境温度高于正常状况或风扇破裂,风速降低,则降低频率或减少活动内核的数量。借助新的缩减式冷却方式来降低器件的功耗可使系统回到热/功率稳定状态。

(图字)功率

图1:功耗如何随温度变化而改变。

现代高频器件所消耗的电量大约有一半是静态功率- 漏电与频率无关,但与电压水平有关,而另一半则是动态功率 – 基于系统负荷,因此与频率及电压有关。静态和动态功率之间的合适比率取决于器件的设计选择数量,如工艺技术、晶体管的选择和布局。但在包含芯片的各个器件之间和芯片之间也存在自然的工艺差异。漏电较多的晶体管功耗一般也更高,以允许更高的最大频率。因此,把器件设置为高速、高功率,或低速、低

- 管理多电压轨系统让数字电源管理变得简单(08-17)

- 具USB OTG和过压保护的紧凑型电源管理器(08-17)

- 设计切实可行的压电能和热能收集方案需考虑的因素(08-23)

- 针对能量收集型无线远程传感器网络的实用电源管理设计(11-29)

- ACPI PC电源管理(05-13)

- 具有USB OTG和过压保护的紧凑型电源管理器的实现(10-17)