基于FPGA的可扩展高速FFT处理器的设计与实现

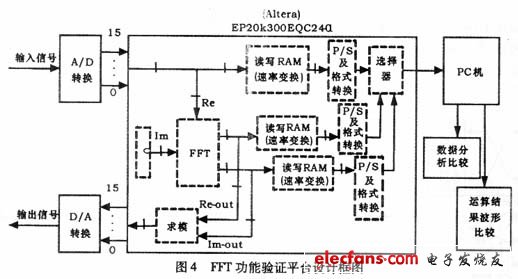

我们利用FPGA实现的各功能模块按图1实现结构组装了8&TImes;4&TImes;2点组合数FFT处理器,通过仿真验证了其设计的正确性后,又在FPGA实验板上对它进行了硬件验证,其实验验证平台如图4所示。

硬件验证时采取的实验方法是,用相同的抽样频率fs等间隔地抽取不同频率单频正弦信号相同点数64点,即固定FFT的频率分辨率fr,利用设计的64点FFT处理器计算其幅度谱,观察其幅度谱中直流分量谱线和谐波分量谱线间隔大小的变化,把实验结果和理论分析结果进行对照,以确认FFT处理器工作的正常与否。

系统时钟工作在 40.861 MHz 时,抽样频率为 40.861/2=20.4305 MHz,抽样周期为1/20.4305 MHz="48".9 ns,抽取64个点的时间是48.9×64=3.13μs。因为每个采样数据间隔时间是48.9μs,所以用设计的流水线方式工作的6

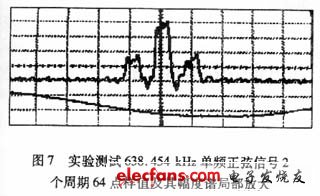

4点FFT处理器计算其幅度谱的谱线间隔也为48.9 ns。当输入单频正弦信号的频率约为638.454 kHz时,其周期为1/638.454 kHz=1.567μs。用20.4305 MHz频率抽样,3.13μs时间内刚好在正弦信号的2个周期内抽取64点,输入单频正弦信号的频率是频率分辨率319.227 kHz的2倍,直流分量为幅度谱的第1根谱线,一次谐波分量为幅度谱的第3根谱线,其理论计算结果波形如图5所示,实验测试结果波形及其的局部放大波形如图6和图7所示。

从示波器上可以看出,横坐标单元格间隔为1μs,FFT变换周期间隔约为3格,即约为3μs,抽取了信号波形的2个周期,64点FFT计算时间也约为3μs。

输入单频正弦信号的频率是频率分辨率319.227 kHz的2倍,直流分量为幅度谱的第1根谱线,一次谐波分量为幅度谱的第2根谱线。由于幅度谱的谱线间隔为48.9 ns,也就是说,直流分量和一次谐波分量间隔约为100 ns。从示波器上可以看出,横坐标单元格间隔为100 ns,直流分量和一次谐波分量间隔约为100 ns,和理论分析结果一致。

四、结论

本文以高组合数混合基DFT算法为基础,设计并用FPGA实现了变换点数可灵活扩展的流水线FFT处理器。输入/输出数据速率为20 MHz时,读/写RAM工作在40 MHz时钟,计算出1 024点FFT的运算时间约为52μs。本设计采用模块化设计结构,便于系统调试和实现,而且各设计模块可以重复利用,避免重复相同的设计,从而缩短芯片设计开发时间,更易于FFT处理器的结构扩展。整个FFT设计结构新颖,实现容易,具有一定实用价值。

- 教你用示波器频域方法分析电源噪声(02-19)

- 利用FFT IP Core实现FFT算法(02-16)

- 示波器频域方法分析电源噪声(07-06)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- XILINX FFT IP的使用(续)(02-11)

- 卫星导航系统基带伪码完整系统解决方案(08-06)