XILINX FFT IP的使用(续)

时间:02-11

来源:网络整理

点击:

四、Symbol与I/O说明

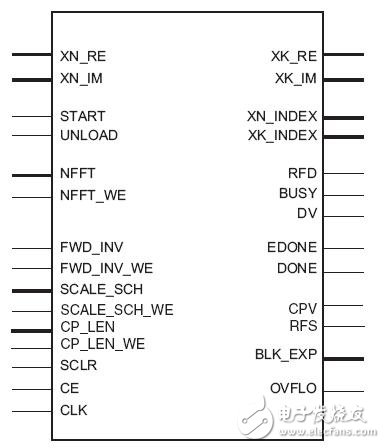

FFI IP的输入输出信号如下图示:

左边为FFT IP的输入信号,右边为FFT IP的输出信号。

具体的引脚说明如下:

1.XN_RE: 输入信号,输入数据总线的实部,以2的补码形式输入,位宽8~24比特。

2.XN_IM: 输入信号,输入数据总线的虚部,以2的补码形式输入,位宽8~24比特。

3.START:输入信号,FFT开始信号,高有效。此信号变高后,开始数据装载与计算。

4.UNLOAD:输入信号,对于Burst I/O结构,此信号将开始输出处理的结果,对于流水线结构和比特逆序输出的情况,此信号是不必要的。

5.NFFT:输入信号,实时配置应用时用来改变变换长度(即点数)。

6.NFFT_WE: 输入信号, NFFT端口的使能信号,高有效。

7.FWD_INV:输入信号,用来指明是计算正变换还是反变换,FWD_INV =1为FFT变换,FWD_INV =0为IFFT变换。

8.FWD_INV_WE:输入信号, FWD_INV端口的使能信号,高有效。

9.SCALE_SCH:输入信号,在IP核设计中,如果选择了在计算过程中进行中间数据的缩减时此信号才有用,输入位宽为2 x NFFT(基2结构和基2 Lite结构)或2 x ceil(NFFT/2) (基4结构和流水线结构), 其中NFFT为变换长度用二进制表示时的宽度。

10.SCALE_SCH_WE:输入信号, SCALE_SCH端口的使能信号,高有效。

11.CP_LEN: 输入信号, Cyclic prefix length, 大小为0~(变换长度-1),在cyclic prefix inserTIon有效时才有用。

12.CP_LEN_WE:输入信号, CP_LEN端口的使能信号,高有效。

13.SCLR:输入信号,可选的异步复位信号,高有效。

14.CE:输入信号,可选的时钟使能信号,高有效。

15.CLK:输入时钟。

16.XK_RE:输出信号,输出数据总线的实部,以2的补码形式输出, SCALE_SCH_WE有效时,输出位宽等于输入,否则输出位宽等于输入位宽+NFFT+1,其中NFFT为变换长度用二进制表示时的宽度。

17.XK_IM:输出信号,输出数据总线的虚部,以2的补码形式输出, SCALE_SCH_WE有效时,输出位宽等于输入,否则输出位宽等于输入位宽+NFFT+1,其中NFFT为变换长度用二进制表示时的宽度。

18.XN_INDEX:输出信号,输入信号的下标。位宽等于变换长度用二进制表示时的宽度。

19.XK_INDEX:输出信号,输出信号的下标。位宽等于变换长度用二进制表示时的宽度。

20.RFD:输出数据有效信号,高有效。

21.BUSY:状态忙指示信号, 正在进行转换时输出高电平。

22.DV:数据有效指示信号,当输出端口存在有效数据时输出高电平。

23.EDONE:提前的DONE信号,高有效,在DONE信号变高前的一个时钟变高。

24.DONE:完成信号,高有效,在FFT完成后变高一个时钟,

25:CPV:Cyclic prefix有效信号,高有效。在cyclic prefix inserTIon有效时才有用。

25:RFS:已经准备号信号,高有效,当RFS变高后才可以开始接收START信号,在cyclic prefix inserTIon和流水线结构中才有用。

26.BLK_EXP:输出信号,在块浮点结构中指出每块数据的缩放率。

27.OVFLO:输出信号,算法溢出指示,在数据输出时,如果该帧有溢出发生,则此信号变高。

上面简单介绍了FFT IP的输入输出信号,大家在定制该IP时可以参考一下。详细说明在定制IP时点帮助按钮可以查看。

- 基于FPGA的可扩展高速FFT处理器的设计与实现(04-25)

- 教你用示波器频域方法分析电源噪声(02-19)

- 利用FFT IP Core实现FFT算法(02-16)

- 示波器频域方法分析电源噪声(07-06)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- 卫星导航系统基带伪码完整系统解决方案(08-06)