基于FPGA技术的存储器设计及其应用

USE_EAB——决定是否使用嵌入式阵列块。

双击双端口RAM参数列表可弹出引脚/参数设置窗口。在引脚/参数设置窗口可以具体对双端口RAM进行引脚、参数设置。可以根据具体的对存储器的功能要求,决定各种口线的使用与否。例如不想使用rdclken(读时钟使能)信号,则可以将其Status设置为Unused即可。同时还可以通过Inversion项设定该信号的初始状态(初始值)。在窗口的Parameters参数设置处,选择不同的参数项后,通过ParameterValue项可以改变或设置其相应的状态或数值。如想设置存储数据为8位宽度,则选择LPM_WIDTH项,然后将Parameter Value设置为8。

例如要设计一个11位宽数据,512个存储单元,使用读写同步时钟、不需要读写使能端及时钟使能端的双端口RAM。则可以打开引脚/参数设置窗口,设置LPM_NUMWORDS为512,LPM_WIDTH为11,LPM_WIDTHAD为9,LPM_INDATA、LPM_OUTDATA、LPM_RDADDRESS_CONTROL和LPM_WRADDRESS_CONTROL为寄存方式,使用嵌入式阵列;rdaddress、rdclock、data、wraddress、wrclock、q为Used,rden、rdclken、wren、wrclken为Unused。

其它存储器的构造方法

不同的存储器根据各自特点,应用场合也不尽相同。ROM存储器主要用来存储"常量",如系统参数、波形发生器的信源等。先进先出FIFO存储器可用于信号的实时不间断采集,存储、缓冲两个异步时钟之间的数据传输等。

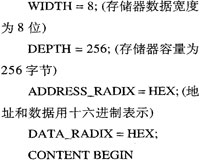

ROM、FIFO等存储器的调用库函数构造方法与双端口RAM的构造方法类似,在mega-lpm库中调用相应的模块单元即可。其中ROM存储器在库中是LPM_ROM模块,FIFO存储器在库中有CSFIFO、DCFIFO、LPM_FIFO、LPM__FIFO_DC、SCFIFO、SFIFO共六种。需要说明的是由于ROM在实际系统运行时的不可写入性,在ROM构造过程中要对ROM存储器进行数据初始化。这一操作是通过设置PLM_FILE项完成的。在引脚/参数设置窗口的Parameters参数设置处选择该项,再通过ParameterValue项确定相应的数据初始化文件(*.mif)即可。下面是VHDL格式的ROM数据初始化文件(文件可用任何文本编辑器实现):

双端口RAM在高速数据采集中的应用

利用传统方法设计的高速数据采集系统由于集成度低、电路复杂,高速运行电路干扰大,电路可靠性低,难以满足高速数据采集工作的要求。应用FPGA可以把数据采集电路中的数据缓存、控制时序逻辑、地址译码、总线接口等电路全部集成进一片芯片中,高集成性增强了系统的稳定性,为高速数据采集提供了理想的解决方案。下面以一个高速数据采集系统为例介绍双端口RAM的应用。

该系统要求实现对频率为5MHz的信号进行采样,系统的计算处理需要对信号进行波形分析,信号采样时间为25μs。根据设计要求,为保证采样波形不失真,A/D采样频率用80MHz,采样精度为8位数据宽度。计算得出存储容量需要2K字节。

根据设计要求,双端口RAM的LPM_WIDTH参数设置为8,LPM_WIDTHAD参数设置为11(211=2048),使用读写使能端及读写时钟。ADCLK、WRCLK和地址发生器的计数频率为80MHz。

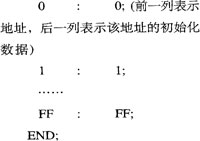

A/D转换值对双端口RAM的写时序为顺序写方式,每完成一次A/D转换,存储一次数据,地址加1指向下一单元,因此写地址发生器(RAM_CONTROL)采用递增计数器实现,计数频率与ADCLK、WRCLK一致以保证数据写入时序的正确性。写操作时序由地址和时钟发生器、A/D转换时钟和双端口RAM的写时钟产生。停止采样时AD_STOP有效,写地址发生器停止计数,同时停止对RAM的写操作。将地址发生器的计数值接至DSP总线可以获取采样的首尾指针。地址发生器单元一般用(VHDL)语言编程实现,然后生成符号文件RAM_CONTROL在上层文件调用。其部分VHDL语言程序如下:

对双端口RAM的读操作采用存储器映像方式,其读出端口接DSP的外扩RAM总线,DSP可随机读取双端口RAM的任一单元数据,以方便波形分析。 由于LPM_RAM_DP模块的读端数据总线q不具有三态特性,因此调用三态缓冲器74244,通过其将输出数据连接到DSP数据总线上。

在高速数据采集电路中,数据缓存也可以用FIFO或单端口RAM实现。用FIFO进行数据缓存,由于其已经把地址发生部分集成在模块单元内,因此省去了一部分程序编写,但是DSP却不能任意地访问FIFO的存储单元,只能是顺序写入/读出数据,这样设计,系统的灵活性就大大降低。如果DSP的分析计算需要特定单元的数据,则系统的效率和速度会因为无效数据的读取而降低。使用单端口RAM进行数据缓存同样存在一些问题。由RAM侧看,DSP和A/D转换器是挂在一条总线上的,当从RAM向DSP传输数据的时候,A

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)