一种高速化和集成化的数据采集系统的设计

随着嵌入式技术的飞速发展,对嵌入式系统的应用需求也呈现出不断增长的态势,因此,嵌入式技术也相应地取得了重要的进展,系统设备不断向高速化、集成化、低功耗的方向发展。现场可编程门阵列FPGA经过近20年的发展,到目前已成为实现数字系统的主流平台之一。 FPGA具有单片机和DSP无法比拟的优势,相对于单片机和DSP工作需要依靠其上运行的软件进行,FPGA全部的控制逻辑是由延时更小的硬件来完成的。

通用串行总线(USB)是现代数据传输的发展趋势,是解决计算机与外设连接瓶颈的有效手段,USB2.O版本在原先的版本基础上实现许多技术上的飞跃与进步。USB2.0协议规范有以下主要优点:1)速度快,接口的传输速度高达480Mh/s,远大于PCI接口的132 Mb/s的传输速度;2)连接简单,所有的USB外设利用通用的电缆可简单方便地连入PC机中,安装过程高度自动化;3)支持多设备连接,USB接口支持多个不同设备采用"级联"方式来连接外设。

故为了将数据采集系统设计更加符合高速化和集成化的趋势,采用了FPGA和USB2.0组合的方案来进行。

1 数据采集系统的框架与硬件设计方案

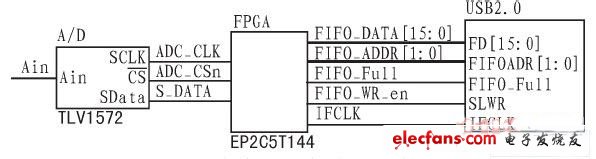

系统硬件设计部分中,在完成系统时钟源、电源等必要电路的设计基础上,重点就是完成系统内各个部件的接口电路的设计,通过这部分的设计,基本的硬件平台就建立起来了。系统部件间的硬件电路接口设计如图1所示。

图1 系统部件间的硬件电路接口设计

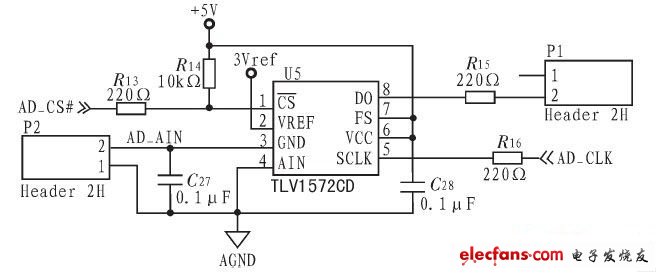

A/D芯片在此选用了德州仪器公司的10位串行接口芯片TLV1572,8管脚的SOIC封装,它外部较少的管脚不仅能够很方便地实现与其他器件连接,而且它体积小,可以节省很多布线资源,如图2所示。TLV1572的最高采样速率为1.25 MS/s,其积分非线性误差INL《±1LSB,可以采用3 V或5 V的供电方式。

图2 A/D芯片及周边电路

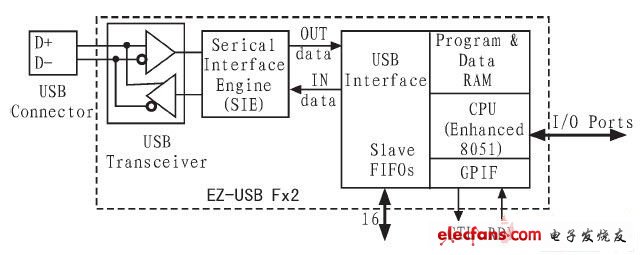

由于大部分USB1.1的芯片都需要微控制器参与数据从端点FIFO到应用环境的转移,微控制器在里面扮演了搬运者的角色,那么显然微控制器本身的工作频率就极大地限制了数据传输带宽的进一步提高,微控制器将成为制约整个系统速度提高的瓶颈。

故在此选用的是Cypress Semiconductor公司的EZ-USBFX2(CY7C68013A)USB2.0芯片,它集成了USB2.0收发器,串行接口引擎SIE和可编程的外围接口。该芯片的另一大优点就是提供了一种独特架构,使USB接口和应用环境直接共享Slave FIFOs,微控制器无需参与数据传输,这样就极大地提高了系统数据传输速率,如图3所示。

图3 EZ-USB FX2芯片的内部结构

由于FPGA的I/O管脚数目众多,它在和A/D芯片及USB2.0芯片相连时,能够按照优化布线资源的方式进行PCB布局设计,具体的连接方法在图1中已经给出。

2 数据采集系统软件设计方案

FPGA软件设计方案中采用了自顶向下的设计方法,运用Verilog HDL语言来设计数字系统,分别完成数字系统内部各个子模块的设计。数据采集系统结构及模块间的连接示意图如图4所示。

图4 数据采集系统结构及模块间的连接示意图

由图4可见,系统主要由3个模块组成。它们分别是A/D接口adc.v模块、USB接口usb.v模块以及顶层top.v模块,其中在顶层top.v模块中,完成了对其他两个模块的调用,使它们拼接成为一个完整的系统。其中锁相环PLL_1和PLL_2分别给ade.v模块和usb.v模块提供时钟源。

2.1 FPGA控制A/D芯片接口的软件设计

在adc.v模块中,需要完成FPGA对TLV1572的接口逻辑代码的设计,其实质就是在TLV1572的时序分析的基础上来设计逻辑代码,使得FPGA能够按照其时序要求完成对A/D芯片的各种控制,包括提供给TLV1572的串行时钟信号信号ADC_CLK、CS片选信号ADC_CSn以及从TLV1572中读取出转换完成的串行数据S_DATA。

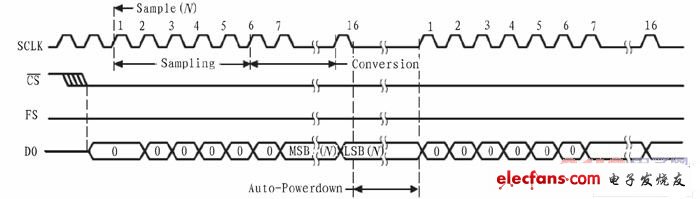

TLV1572的时序图如图5所示。

图5 TLV1572的时序图

从时序图可见,A/D芯片的转化过程是在当CS为低电平后,由SCLK的上升沿发起的,输出的头六位二进制数字均为"0",此时A/D芯片正处于采样阶段,数字无效,这六位无效的二进制数之后,A/D转换完成后的二进制数据在SCLK的上升沿被送到总线上,这时,作为系统主控制芯片的FPGA应当去采样总线上的数据,得到转换后的结果。

2.2 FPGA控制USB2.0芯片的软件设计

在usb.v模块中,需要完成FPGA对CY7C68013A的接口逻辑代码的设计和异步FIFO模块的设计。其中,对CY7C68013A的接口逻辑代码主要是完成对CY7C68013A芯片的端点FIFO的各种控制,包括16位的数据信号FIFO_DATA[15:0]、2位端点FIFO选择信号FIFO_ADDR[1:0]、端点FI-FO满标志位信号FIFO_Full、端点

- 基于计算机的测量仪器的内部和外部校准(10-08)

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于暂态行波法的配电网故障定位装置研究(02-01)

- 数据采集处理系统在电力中的应用设计(12-30)

- 如何通过整合众多特点和性能来解决数据采集兼容性问题(09-15)

- VC串口通信的数据采集系统设计(10-09)