一种高速化和集成化的数据采集系统的设计

FIFO写使能信号FIFO_WR_en。因为adc.v模块和芯片外部的CY7C68013A工作在不同的时钟域内,故异步FIFO模块设计部分设计的目的除了是要完成从ade.v模块读取过来数据的缓冲,另外就是需要解决异步时钟域数据传输可能出现的亚稳态问题。

具体来说,FPGA在工作时需要不断向CY7C68013A的端点FIFO写入数据,而FPGA与CY7C68013A之间的工作模式属于同步方式,两者都由PLL _2模块提供40 MHz的时钟信号进行工作,那么它们之间的关系就是同步Slave FIFO的写操作,由FPGA向CYTC68013A中写入数据。

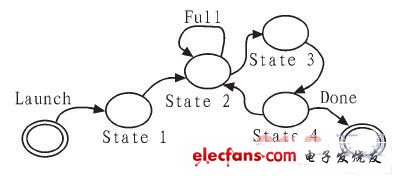

在Verilog HDL程序设计中,需要设计一个状态机来完成同步Slave FIFO写的时序,写时序如下;1)IDLE:当写事件发生时,进状态1;2)状态1:使FIFOADR[1:0]指向IN FIFO,进状态2;3)状态2:如果端点FIFO满,在当前状态等待,否则进状态3;4)状态3:驱动数据到数据线上,使SLWR有效,持续一个IFCLK周期,进状态4;5)状态4:如需传输更多的数,进状态2,否则进入IDLE状态。

该状态转换的状态图如图6所示。

图6 状态转换的状态图

2.3 FPGA的顶层模块的设计

由图4可知,top.v模块是FPGA整个系统的顶层模块,它通过顶层调用的方式把adc.v和usb.v两个模块组合成一个完整的系统,系统与外界进行通信是通过top.v这个模块对外的各个接口来实现的,具体到器件层面,就表现为由top.v文件定义的FPGA的相关的管脚来和A/D与USB2.0芯片进行数据的交换、控制信息以及时钟信号的传递。这种自顶向下的设计方法,不仅符合人的思维逻辑,也大大地简化了大规模逻辑电路的设计工作,使人们从繁琐的自底向上的底层设计中解放出来,以一种系统级的思维模式设计电路。这是自顶向下设计方法的巨大优势之一。顶层top.v模块是通过例化的方式来调用adc.v模块和usb.v模块的以及PLL模块。

2.4 USB2.0芯片的固件程序设计

在USB的体系中,无论是其本身的规范还是各种厂家所提供的芯片资料,关于主机对USB的检测都称之为枚举Enumeration(and ReNumer-ation),即枚举(与重新枚举)。固件在这发挥了无法替代的作用。应该说所有基于微控制器及其外围电路的功能设备的正常工作都离不开固件的参与,固件的作用就是辅助硬件,或者说是控制硬件来完成预期的设备功能。没有固件的参与和控制,硬件设备只是芯片的简单堆砌,无法实现预期的功能。

CY7C68013A内部集成了增强型的8051内核,它与8051指令集二进制是兼容的,那么就可以选择汇编或者高级语言C51来编写固件代码,两者各有优缺点,适用的环境也不同。本设计中采用C51来编写固件程序,关于开发C51语言的Keil μVision 2开发编译环境在此不再赘述。

Cypress公司为了简化和加速用户使用CY7C68013A芯片进行USB外设的开发过程,特别设计了一个完整的固件程序的框架。这个框架可以执行CY7C68013A芯片的初始化、USB标准设备请求的处理和USB挂起电源管理服务。用户只需要提供一个USB描述符表,添加其他端点接收和发送数据的通信代码,以及控制外围电路的程序代码。

在Keil μVision 2集成开发环境下,新建工程后,需要将工程代码复制到工程目录中并添加至工程列表中,开发固件程序需要几个重要的文件依次为:1)fw.c,框架程序的代码。2)periph.c,用户函数挂钩的相关定义,外围设备的控制文件。在上节中,主程序fw.c调用的TD_lnit()函数即在此定义出来。3)dscr.a51,USB描述符表,上节中关于描述符的定义在这个文件中给出。4)EZUSB.lib,EZ-USB函数库目标代码。5)USBJmpTb.OBJ,EZ-USB中断向量和跳转表。6)FX2.h,程序运行所需要的一些宏定义。7)fx2regs.h,CY7C68013A相关的寄存器定义及位屏蔽的宏定义。8)syncdly.h,定义了若干延时函数供程序调用。

3 Modelsim环境下仿真与结果

ModelSim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言的仿真软件,该软件可以用来实现对设计的VBDL、Verilog HDL或是两种语言混合的程序进行仿真,同时也支持IEEE常见的各种硬件描述语言标准。

目前需要对adc.v模块进行功能仿真,以此验证该模块的功能的正确性。仿真测试的方法就是给adc.v这个模块的s_data数据输入端,即A/D芯片的串行数据的输出端,加载一组测试数据,每16个为一组测试数据,模拟在真实环境下从A/D芯片读取出来的二进制数据,然后在adc.v模块的输出端,即并行的16位宽的data_out端口观察是否与给定的测试数据相一致。假如一致,则模块的功能是正确的。假如有个别位的数据不一致,则需要检查模块的代

- 基于计算机的测量仪器的内部和外部校准(10-08)

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 基于暂态行波法的配电网故障定位装置研究(02-01)

- 数据采集处理系统在电力中的应用设计(12-30)

- 如何通过整合众多特点和性能来解决数据采集兼容性问题(09-15)

- VC串口通信的数据采集系统设计(10-09)