智能网络图像监测系统的研究

图像监测在许多领域有着广泛的应用,目前已经安装上的图像监测系统大约60%沿用早期的摄像头加电视和录像带,并采用有线模拟视频传输技术构成。这种方案存在图像质量低、录像带不易保管、资源容易删改、录像机磁鼓寿命短、需专人看管换带、数据的存储量大、查询取证检索和图像压缩后期处理困难等难点。另一方面,有线模拟视频监测存在无线联网、只能以点对点的方式监视现场、布线工程量极大、对距离十分敏感、不能为远程实时监测和中心联网监测提供可扩展性等技术性缺陷。本文提出一种采用FPGA和CMOS数字传感器实现前端数据采集、利用单片机进行图像鉴别和压缩、通过以太网控制器实现图像数据传输的图像监测系统。该系统不仅实现了图像信号数据采集,而且数据传输速度和稳定性高;不仅灵活性好、成本低,而且具有网络化、智能化等优点。

1 系统组成和工作原理

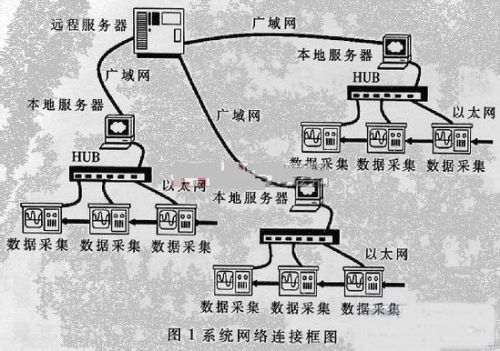

整个图象监测系统采用C/S架构,由本地服务器和多台智能图像采集前端组成分布式网络监测系统。本地服务器和图像采集前端在实现时使用的是自成局域网的方案,采用UDP传输协议和分时轮循管理模式。客户端采集数据,本地服务器处理数据和发送数据。本地服务器之间通过广域网连接,采用FTP传输协议。系统网络连接如图1所示。

嵌入式CPU对采集来的数据进行识别处理,并将有效的图像数据通过以太网卡控制器发送到本地服务器,本地服务器进行图像处理或显示,并向各个终端发送控制信息。同时,本地服务器还决定是否处理过的数据发送到广域网上。

2 图像采集传输系统

图像采集传输系统前端采集图像信号,并将它转化为数字信号,由CPU将这些图像数据通过网络上传到服务器,以供服务器进行图像处理或显示等。同时,服务器也通过网络同图像采集前端发送控制信号、显示信息,向终端查询设备状态、设备信息以及发布网络的辅助协议数据包等。图像采集传输系统包括图像采集存储模块、输入输出模块、电源设计模块、通信模块、红外检测和有效图像识别模块以及其它的附属单元。

2.1 图像采集存储模块

系统的图像传感器选择的是CMOS型高分辨率、高速率彩色图像传感器OV7620。如果用CPU直接从CMOS芯片中采集数据,CPU的速度跟不上,存在着高速外设与低速CPU之间不匹配的问题,因此用FPGA实现图像传感器和CPU之间的速度匹配,如图2所示。FPGA内部可以分为内存分配、产生SRAM的读写时序和地址、为网卡和CMOS提供主频、键盘扩展、产生LCD的控制时序等几部分以及其它附属模块。

FPGA根据CPU的读写信号和CMOS的输出信号产生缓存的读写时序和地址信号。当一帧图像采集完成时,FPGA向CPU发出一个申请信号,表示缓存里面有一帧数据可以进行读取。如果CPU不应答,表示这帧数据可以丢弃。这时FPGA重新根据CMOS图像传感器的输出信号向缓存输送一帧数据,如此循环。如果CPU给出应答信号,FPGA停止向缓存输送数据,等待CPU发送读信号。当CPU发出读信号时,FPGA把CPU的读信号转化为内存的读信号。即FPGA首先根据CMOS的输出数据转化为内存的读信号。

2.2 人机界面设计

2.3 红外检测和图像识别模块

红外检测和有效图像识别模块的作用是减轻网络的负载,使在实际网络中传输的任何连续两帧图像数据不会重复。采用嵌入式CPU进行图像的模式识别,判断连续两帧图像是否有变化。其电路如图4所示。

2.4 RS422通信模块

为了使图像采集前端和其它设备能够进行网际互联,系统挂接了一套全双工总线式RS422串口通讯模式接口电路,满足了传输速率不太高、传输距离远的要求。在实际传输中系统选用的波特率为19200,多机通讯模式,一帧数据长度为11位。

3 嵌入式系统

以太网控制器DM9008F的数据总线是与系统CPU的数据总线直接相连的,通过红外检测的方式判断图像是否有效。为了提高图像数据的导入速度,系统使用的图像数据由高速缓存直接导入DM9008F的环行缓冲区。图像数据不经过CPU,CPU只产生UDP数据报的报文格式信息:报头、目的地址、本机地址等。这种模式的优点是节省了CPU的时间,同时使数据流向显得简单明了。如果通过算法判断图像是否有效,CPU必须实时计算当前帧的图像并判断其是否和前几帧图像的变化程度一致,这时CPU应产生UDP数据报的所有数据。这样虽然提高了判断图像是否有变化的准确率,但浪费了CPU的时间。采用FPGA来产生地址总线的低五位是为了选择网卡内部的工作寄存器。其框图如图5所示。

4 系统软件设计

系统软件包括单片机应用软件、服务器管理软件以及它们之间的通讯协议。单片机软件采用C51和汇编语言联合编写的方式,由主程序、键盘扫描程序、配置CMOS参数子

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)