设计安全工业芯片系统的验证方法

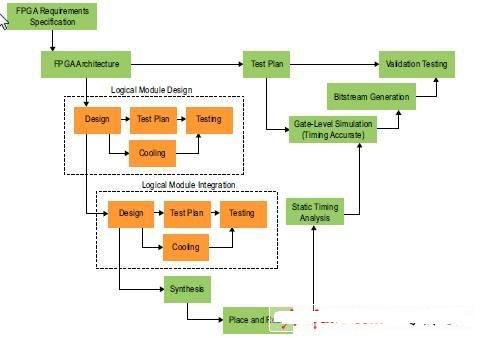

• 循环冗余校验(CRC)计算--用于很多系统中,特别适用于现场总线应用。 • 提取时钟检查--这一内核检查是否有系统时钟以及时钟频率。 • SEU检查控制器--这一模块采用了器件中的内置软错误检查硬件,监视软错误导致的变化。 由于这些硬核IP是在FPGA逻辑区中实现的,因此,系统处理器不再承担这些任务。在认证方法方面,Altera采用了IEC规范,分析了FPGA设计方法和相关要求。从这一分析中,Altera形成了工具流文档。这一工具流的中心主题是对Altera开发的FPGA V-Flow的描述,如图6所示。 图6.工具流 V-Flow及其相关文档将Altera FPGA安全应用设计的所有步骤映射到IEC规范上,满足其要求。此外,它解释了哪些设计步骤采用哪些Altera工具。它涉及到IEC规范中的某些章节,以指导用户依照合适的开发步骤来开发安全应用。 这包括了评估人员所需要的认证文档和数据,以完全符合IEC 61508规范的格式提供,因此,评估人员很容易处理它们。以正确的格式提供这些文档节省了安全工程大量的文档工作。在所包括的可靠性报告中,Altera对Altera FPGA的可靠性统计信息进行了大量的分析,包括所需的全部信息来计算FIT率。 通过重新使用符合预认证两芯片方法的驱动系统概念,按照经过认证的设计方法、设计流程、工具和IP,通常能够加速实现典型的应用开发过程。由于能够立即使用组件的可靠性数据,提供的格式很容易集成到安全认证的所有文档中,因此,加速实现了认证过程。在安全设计和系统设计中,设计人员可以充分利用灵活的FPGA设计集成功能。由于安全已经成为具体应用的关键需求之一,因此,它含在整个概念中,通过满足成本和产品及时面市目标来实现它。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)