5 Gsps高速数据采集系统的设计与实现

其中n为ADC转换位数,ω为ADC转换频率。

如果系统采样频率为5 GHz,转换位数为8位,希望得到的有效位数需要大于6位,则通过信噪比与有效位数关系式:

SNR=6.02xENOB+1.76 dB (2)

可得系统信噪比要大于37.88 dB,从而可以算出时钟抖动需要小于7.82 ps。采样频率越高,则时钟抖动需要的值就会越小。

本设计中,高速ADC芯片工作在单通道模式下,为满足EV8AQ160对高质量采样时钟的要求,这里采用低抖动、低相位噪声锁相环时钟芯片AD9520提供2.5GHz采样时钟。AD9520片内VCO可从2.27GHz调节到2.65GHz,还支持外部3.3V或5V供电,频率高达2.4GHz的VCO/VCXO。 AD9520支持SPI和I2C接口,片内集成一片EEPROM可通过串行接口编程以及保存用于上电复位的用户定义存储器的设置。有4组共12个LNPECL时钟输出,任何一个LVPECL输出在时钟频率不大于250 MHz时均可重新定义为2个CMOS输出,并且在上电时可自动同步所有的输出。AD9520的时钟抖动低至十数量级fs,最高为百数量级fs,可以满足本系统对采样时钟的要求。

为了减小时钟相位的抖动和采样时钟偏移,在时钟电路的PCB设计上还采用阻抗匹配的微带线和对称等长走线,防止高速时钟信号反射,提高时钟的信号质量。时钟信号的驱动电路采用差分PECL电路,PECL器件的电平转换速度快,输出信号抖动小,可以减小ADC时钟的孔径抖动。

2.3 高速ADC与FPGA接口设计

ADC输出8路8 bit 625 Msps低电压差分信号(LVDS)逻辑的数据,在采集系统设计中对与其接口器件的性能要求也较高。Xilinx公司Virtex-6系列型号为XC6VLX240T-1156C的FPGA具有高达200个专用LVDS差分逻辑接收通道,双数据率(DDR)LVDS通道发送数据速率高达1.25 Gbps,接收数据速率也高达1.0 Gbps,能够满足接收EV8AQ160输出数据和逻辑控制的要求。由于ADC的输出和FPGA的输入均设计为LVDS逻辑标准,因此ADC可直接与FPGA相连。Virtex-6系列FPGA内部具有专门的LVDS处理单元,可实现LVDS逻辑的串/并降速转换,降低速率后的数据给到内部分布式处理算法(DPA)单元进行精确处理后存储到内部的存储单元或者外部存储器件DDR3中。当需要对数据进行进一步处理时,通过PCI Express将有效的采集、存储数据发送到上位机,经过软件编程实现采集信号的波形显示。

2.4 上位机软件设计

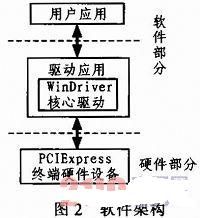

高速数据传输的上位机部分是以PC机为平台进行的软件设计。整个软件架构如图2所示,主要由用户应用程序和驱动程序两部分组成。

上位机系统通过PCI Express接口,控制板卡上的FPGA,并使上位机能够读取到FPGA以DMA方式连续上传的数据,实现上位机内存和FPGA之间数据的高速传输。该软件的驱动部分设计,依靠WinDriver的API函数和已有的PCI Express硬件设备驱动函数,完成对硬件设备的基本控制,为以后软件的进一步升级奠定良好的基础。而用户应用部分,主要是在Visual Studio环境中完成,通过调用可靠的设备驱动函数,成功地通过PCI Express接口与FPGA进行数据通信。

2.5 测试结果

1)ADC与时钟性能测试

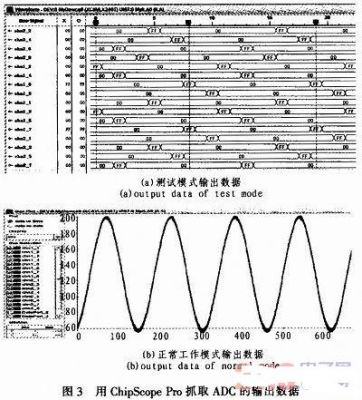

这里采用Xilinx公司ISE软件中的ChipScope Pro工具将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,直接查看ADC输出的数字信号,这些信号在操作系统速度下或接近操作系统速度下被采集,并从编程接口中引出,再将采集到的信号通过ChipScope Pro逻辑分析器进行分析。

首先让ADC工作在采样率为5 Gsps的单通道模式下,用特定的测试模式来检验ADC与FPGA之间的数据接口的准确性。将测试程序下载到FPGA并运行后,用ChipScopePro抓取ADC的输出数据如图3(a)所示。然后在单通道模式下不使用测试模式,输入2MHz的正弦信号,用ChipSco pePro抓取ADC的输出数据如图3(b)所示。

从图3(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图3(b),输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为42.9 dB,由式(2)计算得到ADC的有效位数为6.6 bit。实测表明,AD9520输出的2.5 GHz时钟以及EV8AQ160均具有较高的性能,整体指标达到设计要求。

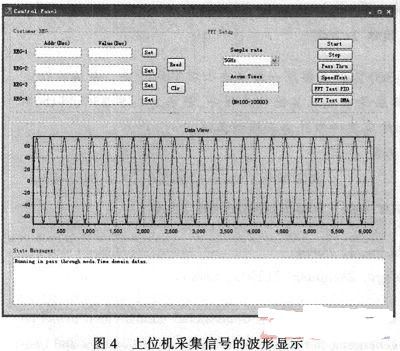

2)上位机数据结果显示

用户应用窗口程序的设计是在Visual Studio 2008环境下进行的,内部通过调用WinDriver提供的API函数及已编写的驱动函数,可以打开、查看、配置和关闭该PCI Express硬件设备。将系统配置为5 Gsps采样率的工作模式,用TeeChart画出实时采集到的波形,如图4所示,表明系统实现了数据的实时采集存储功能。

3 结束语

采用FPGA作为数据采集系统的控制核心,

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)