基于FPGA和MV-D1024E相机的图像采集系统

时间:06-25

来源:尹朝亮,艾勇 武汉大学

点击:

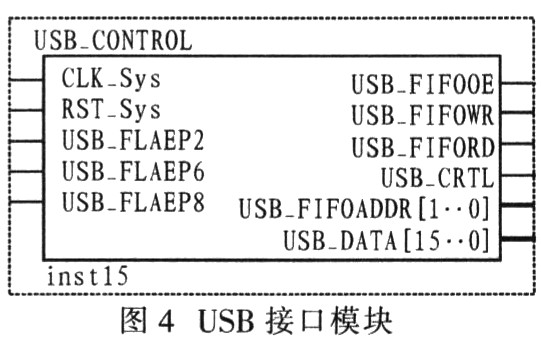

器、串行接口引擎(SIE)和增强型8051微处理器,还包括1个8.5 KB片上RAM、1个4 KB FIFO存储器及1个通用可编程接口(GPIF)。内部RAM运行的8051程序由固化好的外部储存器设备EEPROM提供,与FPGA接口如图4所示。

3.4 USB接口设计

USB接口用于FPGA与PC机间的数据和指令的交换,USB(Universal Serial Bus)是通用串行总线,其具高速度、低成本、低功耗、即插即用和使用维护方便等优点,采用IEEE1394总线协议,最高带宽可达到480 Mb/s。采用Cypress公司的EZ-USBFX2系列器件中的CY7C68013,这是一种基于8051单片机的USB接口主控制器,它集成了USB2.O收发器、串行接口引擎(SIE)和增强型8051微处理器,还包括1个8.5 KB片上RAM、1个4 KB FIFO存储器及1个通用可编程接口(GPIF)。内部RAM运行的8051程序由固化好的外部储存器设备EEPROM提供,与FPGA接口如图4所示。

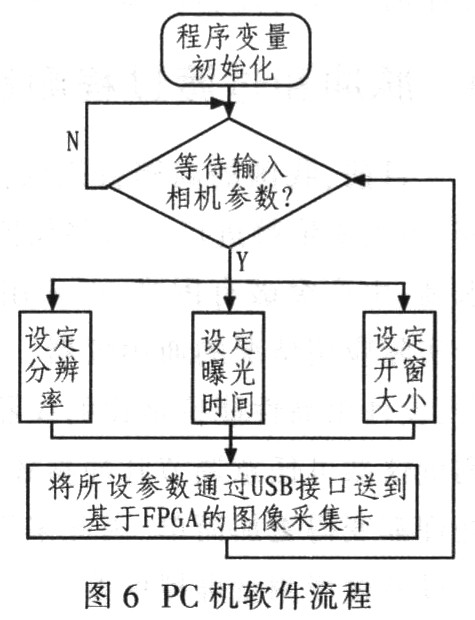

4 PC机软件设计

PC机主要用于用户输入和采集数据的显示,通过Visual C++6.O编译环境开发,结构简单,容易实现。其流程如图6所示,用户通过该界面设置相机的分辨率、曝光时间、开窗大小等参数。

5 结论

应用FPGA实现的图像采集系统,完成了对高帧频CMOS相机的数据接口和控制,用FPGA集成的USB接口,既可采用PC机作为简单的用户输入要求,又可完全脱离PC机,建立脱离PC机的图像采集及处理系统。MV-D1024E系列相机具有12 bit的数据输出,附加相机的时钟PCLK、帧频信号FVAL、行频信号LVAL和数据有效信号DVAL。图3为用FPGA设计生成的相机接口模块,该模块完成相机数据及各时钟信号的接入,并集成串行接口模块,将用户对相机的控制信号发送到相机。完成相机的参数设置功能。

MV-D1024E FPGA CAMERA-LINK 图像采集系统 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)