基于FPGA的低成本虚拟测试系统实现

A实现

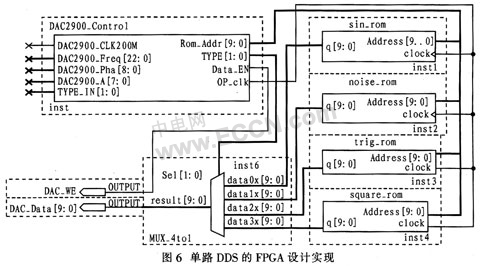

本系统基于FPGA实现双路完全独立的DDS信号源,硬件设计构成了DDS技术实现的第三部分,前面两部分相位累加器和查找表ROM设计细节介绍如图6所示。

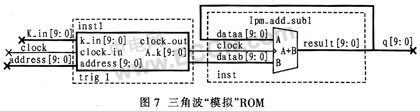

单路DDS的FPGA设计实现主要包括相位累加器地址产生及控制模块、波形存储及类型选择模块。相位累加器地址产生及控制模块对接收到的控制指令实施执行,并产生相应的控制信号、寻址后端LUT ROM,实现DDS信号源。其翻译及执行的信号包括信号类型TYPE_IN、输出信号相位DAC2900_Pha、输出信号频率DAC2900_Freq和输出信号幅度DAC2900_A等。相位累加模块根据输入信号参数,计算并产生地址,用以LUT ROM查找幅度值,输出相位。而波形存储模块分为周期信号产生的正弦信号、锯齿波信号以及方波信号和非周期的高斯噪声信号。其中:sin_rom存储的数据为量化的一个周期的正弦波数据。trig_rom块并不是一个ROM模块,而是一个三角波计算生成模块。为了节省FPGA片内RAM模块,结合三角波的线性特性,利用地址产生三角波幅度值,实现如图7所示,其中K_in[9:0]为产生的三角波波形设定斜率,clock、address和q[9:0]实现与sin_rom接口兼容。square_rom和trig_rom一样,采用Verilog HDL模拟的查找表ROM,可有效减少对FPGA资源的占用,本设计的trig_rom仅占用一个10位加法器。noise_rom为改进型加法同余伪随机序列。数字随机噪声的设计也就是伪随机序列设计,其具有良好的随机性,它的相关函数接近白噪声的相关函数。伪随机序列算法包括:平方取中算法、同余算法、小数开方法、Tausworthe序列。而同余算法包括加法同余数列、线性同余数列和乘进位算法。结合各种算法及其在FPGA上的实现复杂度和资源重用率,设计了易于FPGA实现的改进型加法同余伪随机序列。

结束语

综合考虑成本、性能和应用等因素,充分利用FPGA的逻辑资源,实现了中低档测量系统。双路信号源独立工作可产生最大2 MHz的无失真三角波、正弦波、方波及调制波形等;示波器可虚拟存储采样速率为40 MS/s;逻辑分析仪最高采样频率150 MHz,存储深度256 K×32 bit。适用于教学试验。并协同上位机软件和USB2.0接口实现便携、即插即用。系统预留以太网接口,可实现测量设备网络共享。同时还需进一步提高系统复杂度,充分利用FPGA特点,由上位机动态配置板卡功能。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)