集成电路的电磁兼容测试

集成电路的电磁相容性正日益受到重视。电子设备和系统供货商努力改进其产品以满足电磁兼容规格,降低电磁发射和增强抗干扰能力。过去,集成电路供货商关心的只是成本,应用领域和性能,几乎很少考虑电磁兼容问题。即使单颗集成电路通常不会产生较大的辐射,但它还是经常成为电子系统辐射发射的根源。当大量的数字讯号瞬间同时切换时便会产生许多高频分量。

尤其是近年来,集成电路频率越来越高,整合的晶体管数目越来越多,集成电路的电源电压越来越低,芯片特征尺寸进一步减小,但越来越多功能,甚至是一个完整的系统都能被整合在单一芯片中,这些发展都使芯片级电磁兼容更加突出。现在,集成电路供货商也必须考虑自己产品电磁兼容方面的问题。

集成电路电磁兼容的标准化

由于集成电路的电磁兼容是一个相对较新的学科,尽管对电子设备及子系统已经有了较详细的电磁兼容标准,但对集成电路来说,其测试标准却相对滞后。国际电工委员会第47A技术分委会(IEC SC47A)早在1990年就展开集成电路的电磁兼容标准研究。此外,北美的汽车工程协会也开始制订自己的集成电路电磁兼容测试标准SAE J 1752,主要着重在发射测试部份。1997年,IEC SC47A所属的第九工作组WG9成立,专门研究集成电路电磁兼容测试方法,参考了各国的建议,至今相继出版了150kHz~1GHz的集成电路电磁发射测试标准IEC61967和集成电路电磁抗扰度标准IEC62132。此外,在脉冲抗扰度方面,WG9也正制订相关标准IEC62215。

目前,IEC61967标准用于频率为150kHz~1GHz的集成电路电磁发射测试,包括以下六个部份:

通用条件和定义(参考SAE J1752.1);

辐射发射测量方法─TEM小室法(参考SAE J1752.3);

辐射发射测量方法─表面扫描法(参考SAE J1752.2);

传导发射测量方法─1Ω/150Ω直接耦合法;

传导发射测量方法─法拉第罩法WFC(workbench faraday cage);

传导发射测量方法─磁场探棒法。

IEC62132标准用于频率为150kHz~1GHz的集成电路电磁抗扰度测试,包括以下五部份:

通用条件和定义;

辐射抗扰度测量方法─TEM小室法;

传导抗扰度测量方法─大量电流注入法(BCI);

传导抗扰度测量方法─直接射频功率注入法(DPI);

传导抗扰度测量方法─法拉第罩法(WFC)。

IEC62215标准用于集成电路脉冲抗扰度测试,包括以下三部份,但尚未正式出版:

通用条件和定义;

传导抗扰度测量方法─同步脉冲注入法;

传导抗扰度测量方法─随机脉冲注入法参考(IEC61000-4-2和IEC61000-4-4)。

电磁发射测试标准IEC61967

通用条件和定义

IEC61967的通用条件和定义包含下列几项:

传感器:TEM小室、场探棒等;

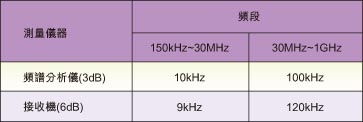

频谱仪或接收机:频率范围覆盖150kHz-1GHz,峰值检波、具备最大值保持功能,分辨率频宽的设置如下表:

表1:分辨率频宽的选择。

电源:用电池供电或采用低射频噪音的电源;

测试温度:23℃±5℃;

环境噪音:除被测IC外其余外围电路供电时,所测到的背景噪音低于限值至少6dB,必要时可采用前置放大器;

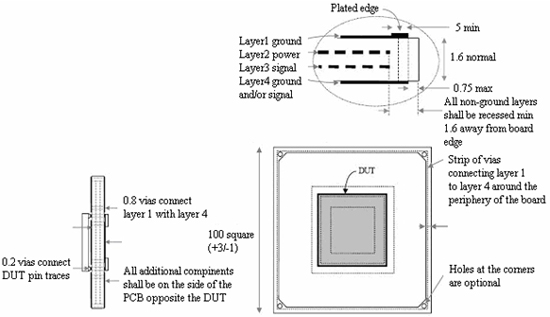

测试电路板:通常集成电路测试需要安装在一块印刷电路板上,为提高测试的方便性与重复性,标准规定了电路板的规格,如下图所示,标准电路板的大小与TEM小室顶端的开口大小匹配,板上既可以整合IEC61967发射测试需要的1Ω/150Ω直接耦合法阻抗匹配网络,磁场探棒法测试用的迹线,也可以整合IEC62132-4用到的耦合电容。

图1:标准集成电路测试板。

TEM小室法

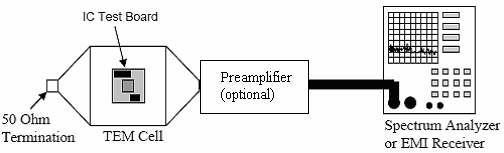

图2:TEM小室法辐射发射测试示意图。

TEM小室其实就是一个变型的同轴线:在此同轴线中部,由一块扁平的芯板作为内导体,外导体为方形,两端呈锥形向通用的同轴组件过渡,一头连接同轴线到测试接收机,另一头连接匹配负载,如下图所示。小室的外导体顶端有一个方形开口用于安装测试电路板。其中,集成电路的一侧安装在小室内侧,互联机和外围电路的一侧向外。这样做使测到的辐射发射主要来源于被测的IC芯片。受测芯片产生的高频电流在互连导线上流动,那些焊接接脚、封装联机就充当了辐射发射天线。当测试频率低于TEM小室的一阶高次模频率时,只有主模TEM模传输,此时TEM小室端口的测试电压与干扰源的发射大小有较好的定量关系,因此,可用此电压值来评定集成电路芯片的辐射发射大小。

表面扫描法

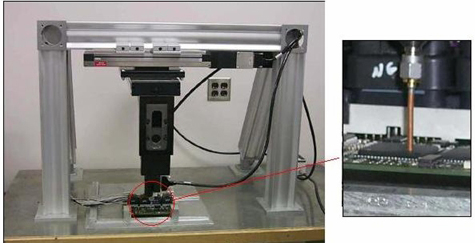

图3:表面扫描法测试图。

- 大容量存储器集成电路测试(12-23)