LCD TV视频解码器技术简介

是MPEG-2 TS或PS/PES,都可以将它们视为最底层的数字数据封包,其地位和角色皆如同以太封包一样,有别于模拟信号。

解码引擎

由于视频、音频格式的多样化,使用单一的解码器已经无法满足这么多的需求。于是有所谓的"解码引擎(decode engine)",它可能是一颗RISC或DSP,负责重置、停止、加载和启动固件或"微码(microcode)",并处理所有与串流解码无关的工作,例如:输出声音。

每个解码引擎内部具有数个解码器,负责下列的工作:1. 开启或关闭单一串流。2. 传送命令。例如:初始化、解除初始化、播放、暂停、停止等。3. 取得目前的状态信息。例如:播放中、已暂停等。4. 各种串流独有的特性。例如:数据格式等。

在这些RISC或DSP内部都具有许多个硬件模块,而每一个模块都具有特定的实体功能;这些功能通常可以利用缓存器(Register)来设定。一般而言,这些RISC或DSP会包含下列的硬件模块:1. 解多任务(Demux)引擎:同时对视频和音频分工。2. MPEG引擎:是一个视频DSP,内含一个视频解码器和一个"子图像(Subpicture)解码器"。3. 音频引擎:是一个音频DSP,内含两个音频解码器和一个混频器(mixer)。4. 中央处理器:CPU核心、DMA、中断处理单元。

这些RISC或DSP的软件模块是利用硬件模块来产生"执行绪(task)"。例如下列的软件模块:1. 系统区块:PLL初始化、DRAM设定……等。2. 图形加速引擎:使用图形加速命令所控制的FIFO,来加快处理速度。3. 字幕解码模块:软件的字幕解码单元。4. I2C:软件的I2C接口,为可程序化的输出入端口(PIO)。5. 内存管理模块:DRAM的配置。

解码引擎的驱动程序

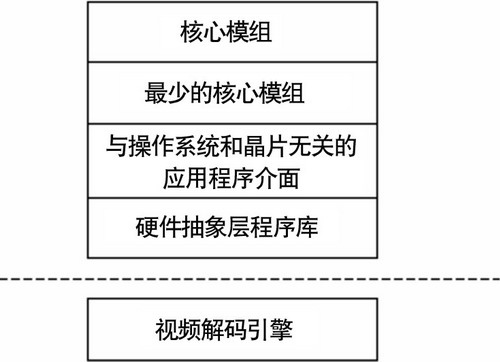

图5 视频解码引擎的驱动程序架构

通常,视频解码引擎的驱动程序会包含下列几个单元(如附图五):1. 与操作系统和芯片无关的应用程序接口(API):控制缓存器和DRAM的存取。2. 硬件抽象层链接库:与硬件相关,可通过XML语言来设定它,以适应特定的芯片。它不包含与操作系统相关的API,只会呼叫与操作系统和芯片无关的API。3. 最少的核心模块:它在上述1.的上方,负责存取缓存器和处理DMA,并且处理OS核心的全部作业,例如:IRQ处理、DMA配置…等。4. 核心模块:它呼叫"最少的核心模块",以存取硬件。

内存的配置

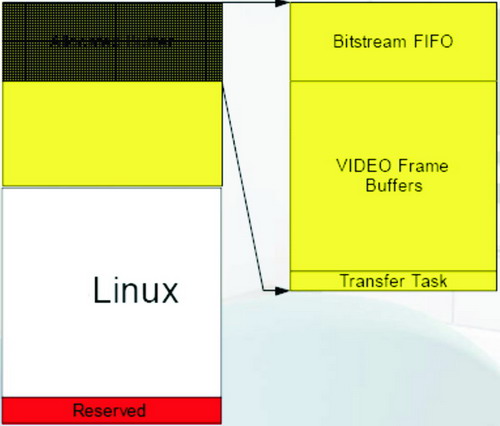

图6 视频解码器的内存配置

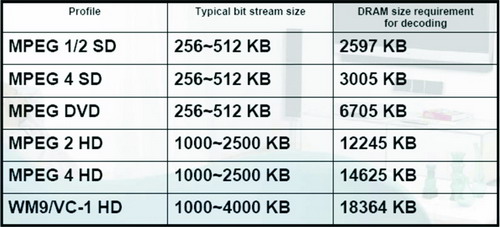

内存配置是在开发视频解码装置时,必须特别考虑的。图6是典型的视频解码器之内存配置;附表一是各种视频格式在解码时所需要的内存大小。

表1 各种视频格式的内存需求

配置内存时,必须避免分割太小和太多。务必先配置大的、长时间使用的缓冲空间(buffer);在进行多信道播放时,应避免不必要的配置或释放缓冲空间。

- 全球液晶显示器Q2增3.1%超预期(08-11)

- OLED显示器及其馈电技术(08-13)

- TFT-LCD光阻回收再利用技术(08-20)

- 关于背投(08-20)

- 薄膜晶体管液晶显示器(TFT-LCD)(上)(08-20)

- 薄膜晶体管液晶显示器(TFT-LCD)(下)(08-20)