在汽车信息娱乐应用中用低成本的PLD管理图像数据

时间:05-30

来源:中电网

点击:

道。

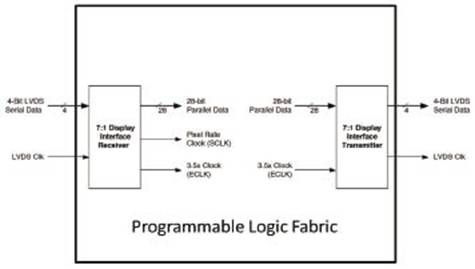

图2 在MachXO2中的接收器和发送器

在此图中,MachXO2器件的接收模块接收四个数据通道,以及通过LVDS I/O缓冲器的时钟。这些缓冲器可以运行高达303兆赫(606 Mbps),支持高分辨率,显示刷新速率高达85 MHz的像素速率(SXGA)。 PLL是用3.5乘以时钟。然后通过一个低偏移边缘的时钟网至DDR捕获寄存器来分配较快的移相时钟(ECLK)。LVDS的数据送入具有7:1匹配功能的DDR寄存器。这个匹配使得I/O数据与高速EDGE时钟(ECLK)解多路复用,然后至较慢速度的FPGA时钟频率(SCLK)。

这个7:1 LVDS的解决方案包括自动对齐PLL输出时钟到最佳位置,用于对输入LVDS数据流采样,为自动对齐可编程逻辑器件的时钟至输入数据字添加逻辑。这些"软"的逻辑与"硬"资源相呼应,提供完整的显示接口解决方案。

MachXO2 PLD的发送模块接收28位并行数据和快速的DDR时钟(ECLK)。并行数据送入到具有7:1匹配功能的显示I / O逻辑单元。匹配功能使得具有低速系统时钟(SCLK)的输入数据复用至更高速度的DDR输出边缘时钟速率(ECLK)。

总结

用许多图像源(几个摄像机)来增加数字内容,后座显示屏和导航系统正在进入主流市场。

在图像应用方面,由于成本和功耗的优势,预计7:1 LVS接口将依然流行,例如车载信息娱乐系统。

MachXO2器件可以部署在汽车辅助驾驶系统来管理来自摄像机的图像的显示和操作(缩放,旋转等)。MachXO2器件可以从一台摄像机到其他摄像机显示图像之间进行动态切换,或将两者组合在一起。

- 如何利用可编程器件设计车用显示系统(08-30)

- 汽车显示器架构中的外部和内部接口及其整合选型(02-22)