汽车运行状况图像监测系统设计方案

众所周知,飞机上的"黑匣子"可以记录飞机的飞行情况,一旦飞机失事,找到"黑匣子"就能知道飞机失事的原因。

汽车上也可以用类似的装置来记录汽车的运行状况,这正是本文要研究的内容,即记录汽车的图像状况,不仅可以记录汽车运行过程中行驶前方或汽车周围的视频图像,而且也可记录汽车静止时前方或周围的视频图像。一旦有交通事故或者人为损坏汽车等情况,利用该系统记录的汽车状况视频图像,可对事故发生时的情况进行分析,就可以准确地认定交通事故发生的原因,也可对损坏汽车的行为加以鉴定。这对于交通事故责任的认定、事故原因的分析、调查和统计等工作以及减少汽车盗窃和汽车破坏事件的发生都具有重要的意义。

系统总体设计方案

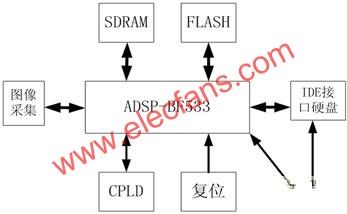

汽车运行状况图像监测系统硬件主要是基于ADSP-BF533芯片进行设计的,设计中分成CPLD电路、图像采集电路、IDE接口电路、SDRAM电路、FLASH电路、电源电路和复位电路等部分。系统整体框图如图1所示。

图1 系统整体框图

1 ADSP-BF533介绍

ADSP-BF533是ADIBlackfin系列最近推出的一款功能强大的DSP,能处理用于互联网的大量图像、声音、文本和数据流,适用于电信和各种互联网设备。ADSP-BF533内核包括2个16位乘法器,2个40位累加器,2个40位算术逻辑单元(ALU),4个8位视频ALU以及1个40位移位器。

2 MPEG-4压缩算法

MPEG-4标准采用了面向对象的视频编码技术。根据面向对象的编码要求,MPEG-4引入了视频对象(VO)的概念。视频对象是可视场景中景物的抽象描述,从用户的角度,它代表画面中任何有意义的物理实体,如人、物体甚至可能是背景。MPEG-4是一个使你由被动变为主动(不再只是观看,允许你加入其中,即有交互性)的动态图像标准。

硬件系统设计

1 存储器电路设计

系统存储器包括数据存储器和指令存储器,其存储器电路由SDRAM与ADSP-BF533接口电路、Flash与ADSP-BF533接口电路组成。

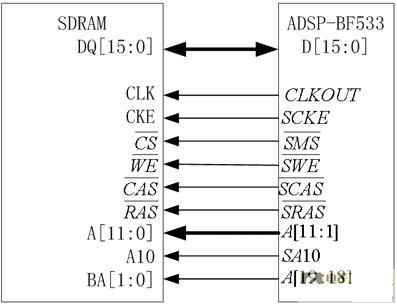

本系统SDRAM采用Hynix公司的HY57V561620。SDRAM与ADSP-BF533的接口如图2所示。

图2 SDRAM与ADSP-BF533的接口电路

HY57V561620是一款高速的同步动态存储器。由于其所有的寻址、刷新等操作都由集成在芯片内部的控制系统完成,因而使用非常简单。HY57V561620的存储空间为32Mb,对于普通的视频应用绰绰有余,并且它加快了存取速度,因此可以在多媒体系统、视频采集与编辑系统等方面广泛应用。

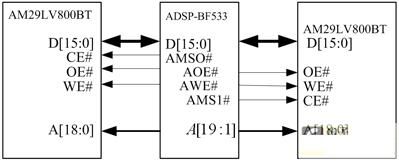

本系统使用2片AM29LV800BT,其BYTE#为8位或16位选择模式引脚,系统使用16位数据模式,所以此引脚接高电平;复位引脚RESET#与CPLD相连。

AM29LV800BT与ADSP-BF533接口图如图3所示。

图3 AM29LV800BT与ADSP-BF533接口电路

AM29LV800BT为1Mb,工作电压为2.7~3.6V,可以被配置为8位或者16位的数据宽度。它共有19个扇区,可以以8位(字节模式)或16位(字模式)数据宽度的方式工作。由于AM29LV800BT内部具有升压电路,因此只需一个3.0V的电源即可完成在系统的编程与擦除操作。通过对其内部的命令寄存器写入符合JEDEC标准的命令序列,可对Flash进行编程(烧写)、整片擦除、按扇区擦除以及其它操作。

2 IDE接口电路设计

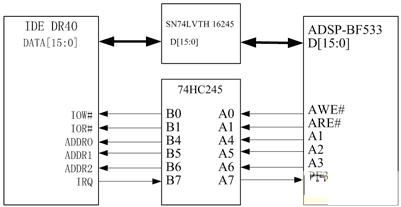

因为ADSP-BF533的数据总线是3.3V的高电平逻辑值,可能出现不能驱动外部SV的逻辑电平的情况,而且连接在数据总线的器件较多,也有可能使数据总线上的驱动能力不足。因此,需要对总线,特别是数据总线进行加强驱动能力的设计,这里数据总线使用SN74LVTH16245来进行双向驱动。SN74LVTH 16245A的功能与74HC245类似,也是通过输出使能(OE)和数据传输方向(DIR)引脚来完成总线隔离与数据传输方向控制功能,不同的是,SN74LVTH 16245A支持16位双向传输,而74HC245支持8位。

IDE接口是一种任务寄存器结构的接口,主机通过访问端口寄存器来读写硬盘。IDE寄存器可分为两组:控制寄存器组和命令寄存器组。在IDE与ADSP-BF533的接口电路中,片选信号TER0、TER1和74HC245的OE连接到CPLD,由CPLD进行逻辑控制。IDE与ADSP-BF533接口图如图4所示。

图4 IDE与ADSP-BF533接口电路

3 图像采集电路

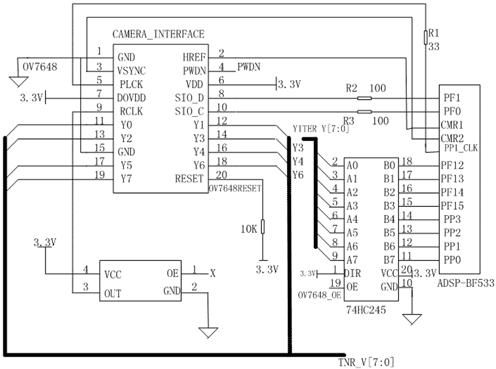

系统外接摄像头,视频图像是通过摄像头的CMOS传感器采集获得的,本系统选用CMOS图像传感器芯片OV7648,它与ADSP-BF533的接口电路如图5所示。

图5 OV7648与ADSP-BF533的接口电路

OV7648芯片通过CAMERA INTERFACE口与ADSP-BF533连接。其中复位引脚RESET与CPLD的OV7648RSET相连;SIO_C、SIO_D是OV7648的I2C总线;XCLK外接一个24.567MHz的晶振,作为OV7648芯片的驱动时钟。

软件系统设计

系统上电以后首先进行自检,然后进行初始化,初始化程序包括对OV7648的设置、PLL、SDRAM和EBIU的设置、

- 基于CAN/GSM的车辆监控系统设计(07-15)

- 基于Zigbee的汽车无线黑匣子设计与实现(10-01)

- ispMACH4000Z CPLD在消费类电子产品中的应用(01-24)

- 如何利用可编程器件设计车用显示系统(08-30)

- 汽车运行状况图像监测系统的设计(09-29)

- 激光扫描车身坐标测量数据采集系统的设计(09-19)