个人多媒体进入车载应用对SoC平台的技术要求分析

下一代信息娱乐系统 表1:RTOS要求和增强功能。

下一代车载信息娱乐系统的基本要求已很明确:高性能、配置性能强以及能够处理多个多媒体数据流。

这些要求显然指向一组辅助属性:高性能数字信号处理、RTOS以及标准化的进程间通信(由保留裕量的软件架构来支持)。

继家庭娱乐模式之后,硬件实现很可能是一个双核心(RISC/DSP)SoC,在上面运行RTOS及专门针对多媒体和流媒体要求而调整的第二个操作系统环境。

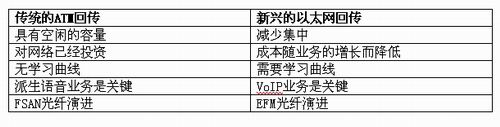

首先考虑RTOS,表1列出了双核心RISC/DSP通信所需的RTOS增强功能。

当然,流式多媒体的软件环境必须与RTOS协同操作--但是其功能却差异很大,因为软件环境是处理流媒体,而流媒体的格式和编解码器变化异于常规。

流媒体软件架构首先是一个组件框架,要求:1.构建和连接组件的协议要统一;2.API一致或相似;3.支持组件同步;4.发展路径清晰。架构的一项关键特性是每个组件都不应该有全局意识。换句话说,I/O可以通过应用程序进行配置。

流媒体也对硬件架构有特殊要求,首先是DSP。例如,VLIW架构就较理想,因为此架构一个时钟周期内可处理多条指令。

多个多媒体数据流需要低延迟方能正常运行,使用此架构则有助于获得更高的工作效率。其他较理想的DSP特征包括:用于计算的硬连接指令、用于快速计算的大寄存器以及额外的特殊内存缓存,以增强性能。

DSP内核--需要VLIW

十几年前,TriMedia内核就将VLIW架构引入商用IC世界,从那以后不断升级。它开始是作为媒体处理器,因此非常适用于汽车信息娱乐计算。

TriMedia采用37个处理单元和128个32位寄存器,每个时钟周期可最多处理5条指令。因此,以300MHz的时钟速度,每秒钟最多可执行100亿次操作。

其集成式内存控制器可以操作处理16MB到256MB的统一标准型DDR SDRAM内存系统。以最高400MHz的时钟速度使用32位宽数据,数据率最高可达1.6Gbps。

如上所述,兼容各种编解码器和格式标准是必需的。

TriMedia内核可兼容所有主流的音频和视频标准,包括MPEG-2、MPEG-4、DV、RealNetworks和DivX-5。对于音频应用,它提供八进制的数字音频输入及S/PDIF(杜比数字)输入和输出。其他几项特性包括:

1. 针对DVD播放功能的32位、33MHz集成式DVD解扰器;

2. 带集成PCI总线仲裁器的MHz PCI 2.2接口,最多4个主接口;

3. 16个专门的通用I/O针脚,适合用作软件I/O针脚、外部中断针脚、用于系统事件计时器/计数器的时钟源/门,以及模拟高速串行协议;

4. 各种视频功能。

RISC内核

RISC内核用作控制器使其功能更为通用。但是,因外围设备很多而且要求苛刻,其性能并不能缩水。RISC内核可运行操作系统、执行某种应用软件、监控系统调试情况,通常还会处理图形用户界面(GUI)。

它还控制I/O块,例如UART、USB内核和蓝牙内核,并处理所有内存管理。

通常选择32位内核,例如ARM926EJ(时钟速度为150MHz或更高,并具有多管道和高速缓存相当大等架构特性),与多数SoC上的DSP共同分担CPU任务。

ARM926EJ结构简图如图1所示。

集成化平台

将DSP和RISC核心以及RTOS与流媒体软件架构集成在一起的平台策略,似乎是车载信息娱乐系统必然的选择。不论对每个组件,还是对平台,娱乐系统专业技术都极为关键。

例如,SoC平台(如飞利浦半导体公司的Nexperia汽车平台)可接收、解码、后期处理并显示具有不同格式的多个视频数据流,包括支持无线电、多通道音频和视频源。

为处理流媒体,需进行以下架构创新:

1. 采用高级通信和同步技术的统一标准内存架构;

2. 确保系统可预测性、易于编程、与ISV协同工作及所承诺的实时行为的基础设施架构;

3. 与硬件架构互补的软件架构。

在Nexperia汽车平台中,ARM内核处理高级OS、控件和应用软件。TriMedia内核处理无线电接收所需的音频和信号处理,以及视频(如果适用)的压缩和解压缩,及其他数据密集型处理任务。两个CPU都是单一集成系统的一部分。

共享统一的内存使其可以有效地通信,以简单的方式共享数据,并可大幅降低内存成本--对于非常占用内存的应用程序效果显著。

每个处理器内核几乎可以寻址任何外围设备--但每个外围设备都分配给其中一个内核的任务域。这样,通过分离应用中的问题(流媒体与控制任务),可保证汽车应用程序实时行为的整体系统性能。

在高层级角度,Nexperia汽车架构包括三个任务域(参见图2)。主干是基础架构,其将外部SDRAM和SoC外围设备连接,以实现高处理量和低延迟访问。

剩余两个域是ARM基础架构,其将ARM内核连接到其域中的外围设备。TriMedia内核采用相同的方法。这使得处理器无需多余的干预,即可执行特定域处理。此外,该基础架构包括连接ARM和TriMedia总线的交叉桥,使每个处理器的内存映射I/O访问能够控制或观察到所有外围设备的状态。

应用图表中定义了不同CPU之间的通信和流路径。它由流框架提供支持,并根据平台要求的处理类型进行配置。根据当时正在处理的数据类型,可以动态创建、连接、配置及破坏专用的信号处理模块。如此便可实现平台的轻松编程和模块的快速集成。

TriMedia流框架和ARM高级OS与基础架构紧密连接,以确保系统的可预测性。根据函数类型,必须针对计时要求进行权衡折衷,例如无线电和TV接收的硬实时状况、视频和媒体支持功能的软实时状况,以及"尽力"获取接入服务。

该基础架构还能够与独立软件供应商(ISV)协同工作,并保证实时行为。这种稳健性在汽车领域是不可或缺的。

Nexperia平台实际上早就参与了下一代DSP/RISC SoC的研究发展,其将信号处理分派给多个内核,每个内核都由专门的硬件加速器提供支持,这些加速器均由设计者使用高级编程语言(如C语言)进行软件配置。

- 利用FPGA协处理器优化汽车信息娱乐和信息通讯系统设计(01-24)

- 汽车收音机TDA7513射频电路应用指南(01-24)

- 基于NI Flex II创新技术的通用仪器可提供最高动态性能(01-24)

- 硬盘驱动器(HDD)新技术瞄准未来数字汽车应用(01-24)

- 当前汽车信息娱乐系统的软件技术需求分析(02-05)

- 联网标准让车载视频娱乐和信息系统成为可能(02-22)