三星和台积电都在搞7nm,英特尔此时发10nm是不是太迟了

过去几个月来,三星、台积电都在不断宣布10纳米甚至7纳米制程上的量产进展,与此对应的是,英特尔10纳米工艺制程的量产计划却一直没有落地,这让英特尔一度遭遇外界质疑。

但就在9月19日,英特尔终于抛出了王炸。

在北京的"英特尔精尖制造日"现场,英特尔一口气对外首次展示了10纳米Cannonlake、10纳米Arm测试芯片、22纳米FFL、14纳米展讯SC9861G-IA和14纳米展讯SC9853I这5款晶圆,对外批露了相关芯片的量产计划,并首次对外详细揭密了自身在下一代制程上的多项前沿技术储备。

会上,英特尔更以少见的强势态度,狠怼"友商"三星和台积电。

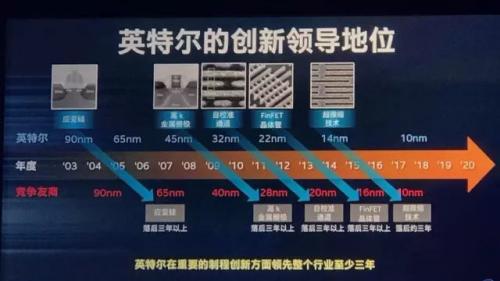

"目前,友商10纳米芯片的晶体管密度,只相当于我们14纳米芯片的密度。"英特尔公司制造、运营与销售集团总裁Stacy J. Smith说,"我们领先了友商整整3年。"

事实上,早在今年3月,英特尔就已在旧金山讲述过同样观点。但在中国这个关键市场再次重申,并展示10纳米晶圆,这被业界视为英特尔发起全面反攻,并加速拓展芯片代工市场的信号。

【摩尔定律不死】

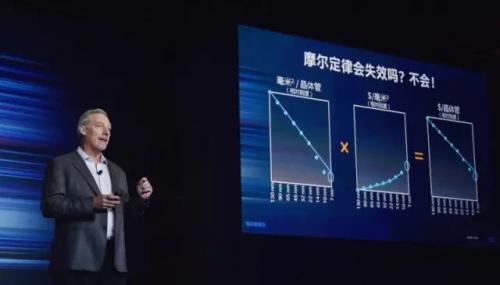

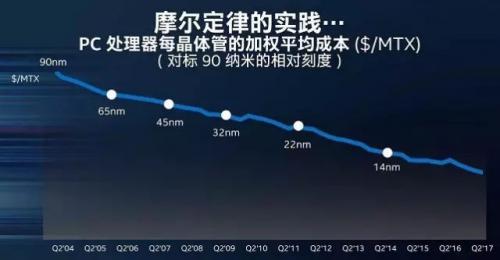

晶体管的制程工艺,多年来一直遵循摩尔定律,即当价格不变时,集成电路上可容纳的晶体管数量,以及消费者每花一元钱能获得的芯片性能,每隔18-24个月便会增加一倍。

但近几年来,摩尔定律还能维持多久,已经成为业界讨论最多的问题。甚至很多分析者认为,摩尔定律即将失效。

其原因在于,我们目前使用的主流芯片制程已经达到14纳米制程,并正在向10纳米发展。而在7纳米以后,晶体管的缩小就将接近物理极限,一旦晶体管进一步降低,就有可能产生量子隧穿效应,为芯片制造带来巨大挑战。

这意味着,如果物理学上没有重大突破,要进一步增加晶体管的密度,就将变得极为困难。

去年,劳伦斯伯克利国家实验室的一个科研团队曾宣称,通过由纳米碳管和二硫化钼(MoS2)的替代材料和技术,已能将晶体管制程的物理极限缩减到1纳米。不过,这一研究目前也还停留在初级阶段。

但英特尔却依然坚定表态:摩尔定律不死。

"诚然,有一天我们可能会达到物理极限,但目前还看不到终点,而摩尔定律在任何可预见的未来都不会终结。"Stacy J. Smith说。

(Stacy J. Smith)

为什么摩尔定律不会失效?

英特尔的答案是,用制程技术之外的"黑科技",来抵消制程技术放缓带来的影响。

比如,应变硅、高K金属栅极、自校准通道、鳍式场效应(FinFET)晶体管等技术,都曾在不同的制程阶段,为缩小晶片面积、提升晶体管密度起到巨大作用。

这样,虽然每一代制程节点之间的时间在延长,但通过超微缩等前沿技术,英特尔可以加速推进晶体管密度的提升,从而确保芯片的性能持续提升和成本持续下降。

(本文资料配图均来自英特尔官方资料)

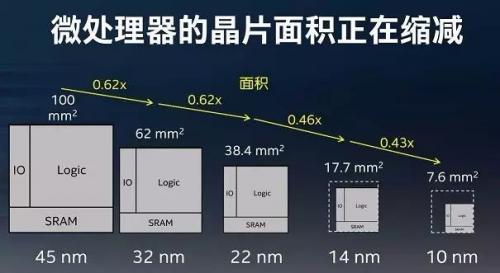

现在,通过超微缩技术,14纳米和10纳米的晶体管密度,都能比以往的制程技术分别提升2.5倍和2.7倍。

这意味着,英特尔能让10纳米芯片的面积缩小到7.6平方毫米,较14纳米芯片缩小了57%,并可以在每平方毫米的面积里,容纳超过1亿个晶体管。

"如果按单个晶体管成本计算,我们的价格下跌速度,甚至还要略快于历史水平。"Stacy J. Smith说。

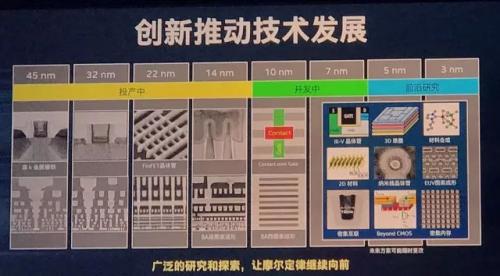

根据Intel的工艺路线图,10纳米制程节点将包括10nm、10nm+、10nm++三个小迭代,其后就将转向7纳米制程,并且5纳米和3纳米也已经在规划中。

在这些阶段,英特尔正对多项前沿技术进行研究和布局,9月18日披露的技术包括:

(1)纳米线晶体管:纳米线结构可改进通道静电,进一步实现晶体管栅极长度的微缩。

(2)III-V 材料(如砷化镓和磷化铟):可以改进载流子迁移率,让晶体管在更低电压和更低的有功功耗下运行。

(3)硅晶片的3D堆叠:可以在更小的面积内,实现不同的技术混装集成。

(4)高密度内存:包括易失性和非易失性存储技术。

(5)高密度互联:将包括新的材料和图案成形技术。

(6)极紫外(EUV)光刻:将在现有的193纳米波长工具基础上,进一步微缩为13.5纳米波长

(7)自旋电子(Beyond CMOS):在CMOS到达微缩极限后,继续提高密度和降低功耗。

(8)神经元计算:采用不同的处理器设计和架构,以更高的能效执行某些计算功能。

【10纳米落地,怒怼三星台积电】

技术密集、资金密集的芯片业,注定是一个寡头竞争的天下。

经过多年厮杀,半导体行业中有能力制造最先进芯片的公司已经屈指可数。在10年前,有18家公司拥有自己的晶圆厂,但现在,这个数字已经减少到英特尔、三星、台积电、格罗方德4家。

"其中,只有3家在投资开

- 英特尔总裁唱衰晶圆代工业(02-23)

- ARM手机芯片市场份额已超90% 英特尔倍感压力(03-17)

- 中国正探寻如何快速进驻HPC芯片领域(03-23)

- 业界不惧英特尔3D晶体管来势汹涌(05-09)

- 第一季度全球20大芯片厂商排行榜出炉 (05-20)

- Q1全球20大芯片厂商排行榜出炉 英特尔夺回优势(05-20)