TI KeyStone II SoC详细介绍

32KB of L1 Instruction cache. The up to four Cortex A15 cores in the ARM CorePac share a 4MB L2 Cache. In the DSP CorePac, in addition to 32KB of L1 program and 32KB of L1 data cache, there is 1MB of dedicated memory per core that can be configured as cache or as memory mapped RAM. The device also integrates 2MB of Multicore Shared Memory (MSMC) that can be used as a shared L3 SRAM. All L2 and MSMC memories incorporate error detection and error correction. For fast access to external memory, this device includes a 64-bit DDR-3 (72-bit with ECC support) external memory interface (EMIF) running at 1600 MTPS.

The device enables developers to use a variety of development and debugging tools that include GNU GCC, GDB, Open source Linux, Eclipse based debugging environment enabling kernel and user space debugging using a variety of Eclipse plug-ins including TI's industry leading IDE Code Composer Studio.

1.4功能框图

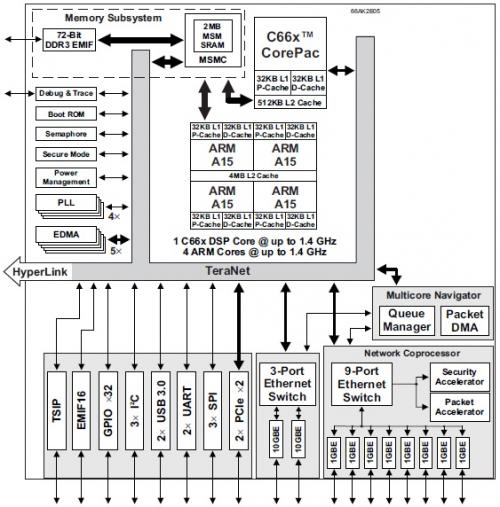

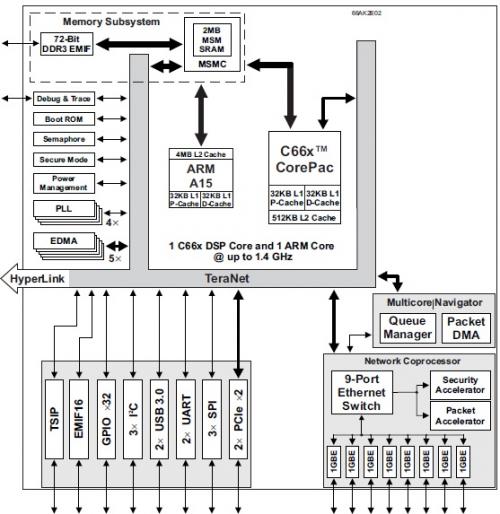

The figures below show the functional block diagrams of the 66AK2E05/02 devices.

Figure 1-1 66AK2E05 Functional Block Diagram

Figure 1-2 66AK2E02 Functional Block Diagram

1.5设备特点

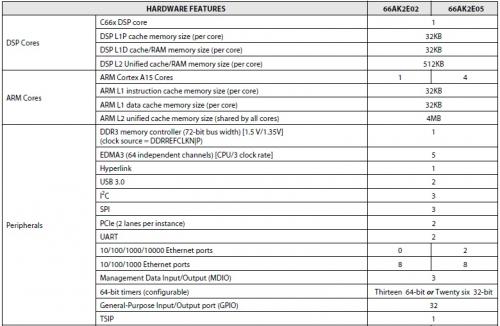

Table 1-1 provides an overview of the 66AK2E05/02 device. The table shows the significant features of the device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count.

Table 1-1 Characteristics of the 66AK2E05/02 Processor

1.6 C66x DSP 核心

The C66x DSP CorePac extends the performance of the C64x+ and C674x CPUs through enhancements and new features. Many of the new features target increased performance for vector processing. The C64x+ and C674x DSPs support 2-way SIMD operations for 16-bit data and 4-way SIMD operations for 8-bit data. On the C66x DSP, the vector processing capability is improved by extending the width of the SIMD instructions. C66x DSPs can execute instructions that operate on 128-bit vectors. The C66x CPU also supports SIMD for floating-point operations. Improved vector processing capability (each instruction can process multiple data in parallel) combined with the natural instruction level parallelism of C6000 architecture (e.g., execution of up to 8 instructions per cycle) results in a very high level of parallelism that can be exploited by DSP programmers through the use of TI's optimized C/C++ compiler.

For more details on the C66x CPU and its enhancements over the C64x+ and C674x architectures, see the following documents (1.9 "Related Documentation from Texas Instruments"on page 15):

• C66x CPU and Instruction Set Reference Guide

• C66x DSP Cache User Guide

• C66x CorePac User Guide

1.7 ARM 核心

The ARM CorePac of the 66AK2E05/02 integrates a Cortex-A15 Cluster (4 Cortex-A15 processors) with additional logic for bus protocol conversion, emulation, interrupt handling, and debug related enhancements. TheCortex-A15 processor is an ARMv7A-compatible, multi-issue out-of-order, superscalar pipeline with integrated L1 caches. The implementation also supports advanced SIMDV2 (Neon technology) and VFPv4 (Vector Floating Point) architecture extensions, security, virtualization, LPAE (Large Physical Address Extension), and multiprocessing extensions. The quad core cluster includes a 4MB L2 cache and support for AMBA4 AXI and AXICoherence Extension (ACE) protocols. For more information see the ARM CorePac User Guide for KeyStone II Devices User Guide listed in 1.9 ‘‘Related Documentation from Texas Instruments’’ on page 15.

1.8 开发工具

1.8.1开发支持

In case the customer would like to develop their own features and

KeyStone II TI 66AK2E05 DSP Cortex-A15 相关文章:

- TI多内核DSP强势反攻FPGA市场(01-16)

- TI KeyStone II为基站处理注入强劲动力 功耗仅为传统RISC内核一半(02-13)

- 德州仪器KeyStoneII架构助力构建绿色环保基站异构网络(03-02)

- 德州仪器KeyStone II架构助力多内核技术发展(01-29)

- 德州仪器推基于多内核DSP的实时JPEP2000高清解决方案(03-20)

- 充分发挥多核优势(08-06)