大批三星、台积电先进制程藏猫腻,英特尔10nm才是业界良心?

时间:03-02

来源:太平洋电脑网

点击:

随着Galaxy S8/S8+的发布,次世代移动平台骁龙835、Exynos8895正式面世,并将10纳米工艺节点推向大规模商用。别急好事多磨--迟到的Intel表示有些不服气了。

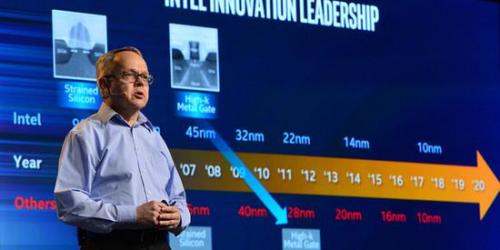

日前,Intel在旧金山举办了"技术与制造日"活动,主管制造、运营和销售的执行副总裁Stacy Smith重申"摩尔定律不死"。根据Intel的工艺路线图,14纳米之后就是10纳米节点,包括10nm、10nm+、10nm++三个小迭代。接着转向7纳米节点,并且5纳米制程可以期待了。

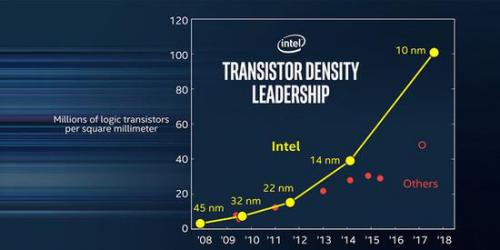

老司机Intel苦口婆心地批评台积电、三星的工艺数字经过"美化",掩盖了栅极间距、晶体管密度等关键指标,自家14纳米工艺足以匹敌友商最新的10纳米工艺。

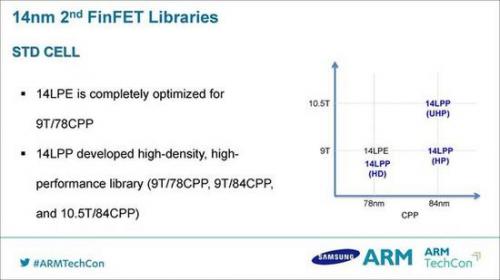

14纳米FinFET工艺下,三星栅极、鳍的间距为84/78纳米、78纳米,大于Intel的70纳米、64纳米;10FinFET纳米工艺下,三星栅极间距为64纳米,大于Intel的54纳米。

而Intel姗姗来迟的10纳米工艺,其晶体管密度将是14纳米的2.7倍,制造成本比友商少30%。

"Intel,你家的10纳米制程又迟到了哦。"

"我们是业界最好的,管用三年!"

- 台积向英特尔宣战 全面追赶10纳米制程(04-24)

- 联发科10纳米内功已超车高通?(01-22)

- AMD 10nm工艺已“亮剑”,英特尔居然一点也不慌(04-27)

- 摩尔定律又发出终结“信号”,只因10纳米成品率太低?(02-15)

- 说说联发科这三年,X10芯片到X30芯片的“高端梦”(06-18)

- 台积电头疼的事情来了,传三星已获苹果A12处理器订单(06-20)