艳压CPU、GPU、ASIC,微软中意的FPGA到底有什么好?

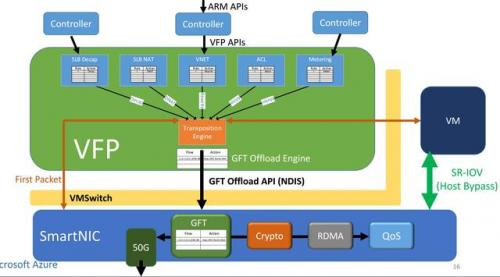

IOV 直接访问这块虚拟网卡。原本在虚拟交换机里面的数据平面功能被移到了 FPGA 里面,虚拟机收发网络数据包均不需要 CPU 参与,也不需要经过物理网卡(NIC)。这样不仅节约了可用于出售的 CPU 资源,还提高了虚拟机的网络性能(25 Gbps),把同数据中心虚拟机之间的网络延迟降低了 10 倍。

网络虚拟化的加速架构

这就是微软部署 FPGA 的第三代架构,也是目前"每台服务器一块 FPGA"大规模部署所采用的架构。FPGA 复用主机网络的初心是加速网络和存储,更深远的影响则是把 FPGA 之间的网络连接扩展到了整个数据中心的规模,做成真正 cloud-scale 的"超级计算机"。第二代架构里面,FPGA 之间的网络连接局限于同一个机架以内,FPGA 之间专网互联的方式很难扩大规模,通过 CPU 来转发则开销太高。

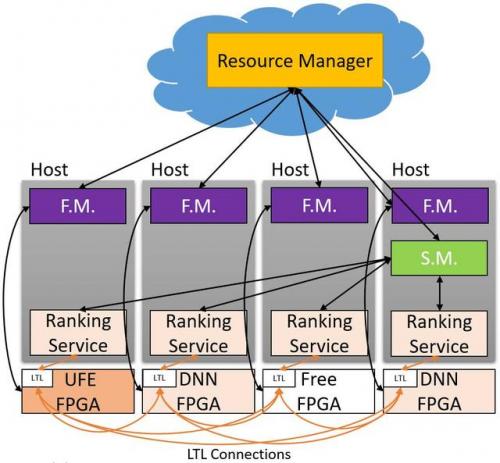

第三代架构中,FPGA 之间通过 LTL (Lightweight Transport Layer) 通信。同一机架内延迟在 3 微秒以内;8 微秒以内可达 1000 块 FPGA;20 微秒可达同一数据中心的所有 FPGA。第二代架构尽管 8 台机器以内的延迟更低,但只能通过网络访问 48 块 FPGA。为了支持大范围的 FPGA 间通信,第三代架构中的 LTL 还支持 PFC 流控协议和 DCQCN 拥塞控制协议。

纵轴:LTL 的延迟,横轴:可达的 FPGA 数量

FPGA 内的逻辑模块关系,其中每个 Role 是用户逻辑(如 DNN 加速、网络功能加速、加密),外面的部分负责各个 Role 之间的通信及 Role 与外设之间的通信

FPGA 构成的数据中心加速平面,介于网络交换层(TOR、L1、L2)和传统服务器软件(CPU 上运行的软件)之间

通过高带宽、低延迟的网络互联的 FPGA 构成了介于网络交换层和传统服务器软件之间的数据中心加速平面。除了每台提供云服务的服务器都需要的网络和存储虚拟化加速,FPGA 上的剩余资源还可以用来加速必应搜索、深度神经网络(DNN)等计算任务。

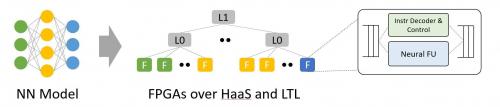

对很多类型的应用,随着分布式 FPGA 加速器的规模扩大,其性能提升是超线性的。例如 CNN inference,当只用一块 FPGA 的时候,由于片上内存不足以放下整个模型,需要不断访问 DRAM 中的模型权重,性能瓶颈在 DRAM;如果 FPGA 的数量足够多,每块 FPGA 负责模型中的一层或者一层中的若干个特征,使得模型权重完全载入片上内存,就消除了 DRAM 的性能瓶颈,完全发挥出 FPGA 计算单元的性能。当然,拆得过细也会导致通信开销的增加。把任务拆分到分布式 FPGA 集群的关键在于平衡计算和通信。

从神经网络模型到 HaaS 上的 FPGA。利用模型内的并行性,模型的不同层、不同特征映射到不同 FPGA

在 MICRO’16 会议上,微软提出了 Hardware as a Service (HaaS)的概念,即把硬件作为一种可调度的云服务,使得 FPGA 服务的集中调度、管理和大规模部署成为可能。

Hardware as a Service (HaaS)

从第一代装满 FPGA 的专用服务器集群,到第二代通过专网连接的 FPGA 加速卡集群,到目前复用数据中心网络的大规模 FPGA 云,三个思想指导我们的路线:

硬件和软件不是相互取代的关系,而是合作的关系;

必须具备灵活性,即用软件定义的能力;

必须具备可扩放性(scalability)。

三、FPGA 在云计算中的角色

最后谈一点我个人对 FPGA 在云计算中角色的思考。作为三年级博士生,我在微软亚洲研究院的研究试图回答两个问题:

FPGA 在云规模的网络互连系统中应当充当怎样的角色?

如何高效、可扩放地对 FPGA + CPU 的异构系统进行编程?

我对 FPGA 业界主要的遗憾是,FPGA 在数据中心的主流用法,从除微软外的互联网巨头,到两大 FPGA 厂商,再到学术界,大多是把 FPGA 当作跟 GPU 一样的计算密集型任务的加速卡。然而 FPGA 真的很适合做 GPU 的事情吗?前面讲过,FPGA 和 GPU 最大的区别在于体系结构,FPGA 更适合做需要低延迟的流式处理,GPU 更适合做大批量同构数据的处理。

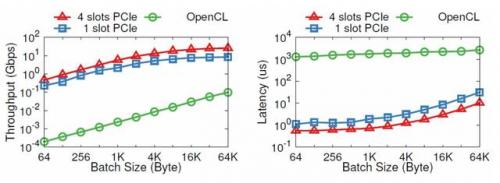

由于很多人打算把 FPGA 当作计算加速卡来用,两大 FPGA 厂商推出的高层次编程模型也是基于 OpenCL,模仿 GPU 基于共享内存的批处理模式。CPU 要交给 FPGA 做一件事,需要先放进 FPGA 板上的 DRAM,然后告诉 FPGA 开始执行,FPGA 把执行结果放回 DRAM,再通知 CPU 去取回。CPU 和 FPGA 之间本来可以通过 PCIe 高效通信,为什么要到板上的 DRAM 绕一圈?也许是工程实现的问题,我们发现通过 OpenCL 写 DRAM、启动 kernel、读 DRAM 一个来回,需要 1.8 毫秒。而通过 PCIe DMA 来通信,却只要 1~2 微秒。

PCIe I/O channel 与 OpenCL 的性能比较。纵坐标为

- 嵌入式系统与FPGA的最新动向(05-18)

- FPGA走向硅片融合时代(07-12)

- 20nm时代,FPGA或将拔得头筹(11-30)

- 没有退路的FPGA与晶圆代工业者(01-03)

- 电源管理成为FPGA新的技术突破口(12-16)

- 数字电源为FPGA带来高效率(12-16)