处理器史话 | 大小核的发展:大四核?小四核?这款CPU到底是几个核?

关于手机的CPU频率描述如下:"大四核2.6GHz,小四核2.1GHz"。

大四核?小四核?这款CPU到底是几个核?

答案:4+4=8,八核!

虽然在核的数量是4+4,但是大核和小核的分工是不一样的,详情如下:

主处理器2.6G四核,用于运行型程序; 协处理器2.1G四核,处理些普通应用程序,比较省电。这就是所谓的八核手机。

为什么要这样设计呢?

原因很简单:CPU没有频率自动调节功能,只能采用高性能4核+低性能4核的组合来延长续航时间,负载高的时候用高性能4核"跑",负载低的时候低性能4核"跑"了。

Smart!给这样的设计点个赞吧!

1. 大小核处理器的问世

三星电子于2013年1月9日(周三)在CES展会上发布了用于智能手机和平板电脑的Exynos 5 Octa处理器。该处理器芯片实际上是在一个芯片封装中包含两个四核芯片,这种8核处理器使用一种新的架构,能够在不减少电池使用寿命的情况下提供更多的性能。四个高性能内核用于游戏和视频重放等繁重的任务。四个功能不太强大的内核用于文本和电子邮件等节能的普通的任务。

三星Exynos 5 Octa发布(图片来自christianpost)

Exynos 5 Octa内部的A15和A7架构处理核心都采用自家的28nm HKMG工艺打造,A7核心主频介于200MHz至1.20GHz之间,A15核心则是200MHz至1.8GHz,两颗CPU都有独立的电源门控制。

随着Samsung S4的问世,全球首款双四核移动处理器(并不能算是真正意义上的八核,因为八个CPU并不是同时工作,而是分为两个四核分别运作)正式登场,基于ARM的ARM big.LITTLE/Cortex A15架构(也就是所谓的大小核架构),号称是一种低功耗,高性能的移动处理器架构。它的大小分别为主频在1.8GHz的A15处理器,负责处理整段的高负荷任务;A7主频为1.2GHz的处理器负责碎片化的轻量级任务。

"这款双四核处理器的具备低功耗和高性能的特色,其3D性能将达到市面所有产品的两倍之多。"--来自三星的宣言。

S4是成功验证了CPU"大小核"的设计的先进性,那么这个设计的灵感来自于哪里呢?

2. 异步多核的思想

很多读者对移动CPU的异步多核的概念不是很理解,它作为高通骁龙系列的一大特色,它和同步多核处理器之间又有什么区别?各有什么优势呢?异步多核处理器又是怎么达到节能目的?与三星Exynos 5440这一类"大小核"的处理器又会有什么差别呢?

异步多核,或者叫aSMP(asynchronous SMP),是由高通提出的,并应用在自家的Snapdragon S3/S4处理器中。之前也有过不少争论,比如:

观点一:异步多核核心之间不能通讯,称之为"胶水双核";

观点二:异步多核同时只能有一个核心接受指令,效率很低。

究竟孰是孰非?

这些实际上都是不对的,Sure!

首先来回答:什么是异步多核?

异步多核,其重点在于频率异步,可以将它称为异步频率架构(Asynchronous Clock Architecture)。在这样设计的多核处理器中,每个核心都可以工作在不同的电压和频率下。这样,可以将计算繁重的任务交给一个工作在高频的核心,而压力较小的任务则可以让一个工作在低频的,较慢的核心去负担。而在同步多核中,所有的核心都只能工作在相同的电压和频率下。

还是不理解?那么请看下面的实例:

如下图所示,当有两个任务,一个计算负荷较重,而另一个计算负荷较轻时(图中紫色部分表示任务的计算负荷),异步多核可以让负荷较重的核心CPU0工作在较高的频率(图中蓝色部分代表频率),而负荷较轻的核心CPU1工作在较低的频率和电压下,由此来减小功耗。

而同步多核的CPU1虽然负荷较轻,但由于架构限制,只能和CPU0保持同样的高频率和高电压,由此浪费了更多的能量,而在高通实际的设计中,不仅多个核心可以工作在不同的电压和频率下,它们共享的L2缓存也可以根据实际的负荷,工作在一个单独的电压和频率下,从而最大限度的节能。

相同任务下的同步多核与异步多核的功耗比较

异步多核架构看上去确实很美好,但实际上并不是完美的。在一些情况下,异步频率架构会发生性能的损失:

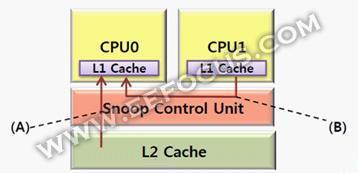

一种情况是,当一个CPU的L1缓存没有命中,需要去L2缓存取数据时,由于异步多核架构的各个核心和L2缓存工作在不同的频率下,需要更多的时间去完成数据的传输,如图中A的箭头所示。例如高通S4,其Krait CPU核心可以工作在最高1.5GHz下,而L2缓存的最高频率为1.3GHz,如果L2缓存处于频率更低的节能状态,此时核心就需要等待L2缓存完成传输

另一种情况下会损失更多的性能。当其中一个核心,例如CPU0的L1缓存没有命中,需要的数据在CPU1的L1缓存时,则数据需要从CPU1的L1缓存传输到CPU

- 第一款处理器之谜(01-29)

- 处理器的春秋战国时代:8位处理器的恩怨与纷争(上)(02-18)

- 处理器的春秋战国时代:8位处理器的恩怨与纷争(下)(02-25)

- 处理器的三国时代:苹果搅动MCU江湖(03-01)

- 处理器的三国时代:DR公司盛气凌人,IBM转身成就微软(03-06)

- 32位处理器的攻“芯”计:英特尔如何称霸PC江湖?(03-15)