利用布线技巧提高嵌入式系统PCB的信号完整性

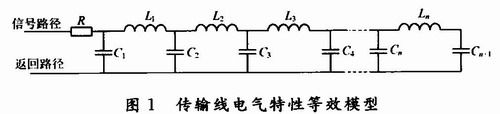

对于均匀导线,在不考虑外部环境变化的情况下,电阻R、传输线寄生电感L和寄生电容C平均分布(即L1=L2=…=Ln;C1=C2=…=Cn+1)。假设传输线为无损传输线,即R=0时,若取线参数:单位长度电容C1、单位长度电感量L1和传输线的总长度为Len,则有:

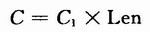

传输线总电容:

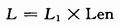

传输线总电感:

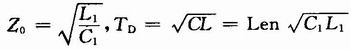

根据传输线的线参数和总长度,可计算传输线的特性阻抗Z0和时延TD,公式如下:

由以上公式可以明显看出,增大电容,减小电感,可以减小特性阻抗;减小传输线总长度,以及电容、电感,均可以减小信号线上的传输时延。

2.2 高速PCB中过孔的电气特性分析

过孔,通常是指印刷电路板中的一个孔,它是多层PCB设计中的一个重要因素。过孔可以用来固定安装插接元件或连通层问走线。从工艺层面来看,过孔一般分为三类:盲孔、埋孔和通孔。盲孔是指位于印刷线路板的顶层和底层表面,具有一定深度,用于表层线路与下面内层线路的连接,孔的深度与孔径通常不超过一定的比率。埋孔是指位于印刷线路板内层的连接孔,它不会延伸到线路板的表面。通孔穿过整个线路板,可用于实现层间走线互连或作为元件的安装定位孔。由于通孔在工艺上更易于实现,成本较低,所以一般印制电路板均使用通孔,而不用另外两种过孔。以下所说的过孔,均作为通孔考虑。

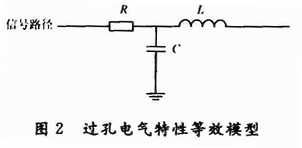

过孔作为一段特殊的传输线,在高速电路中,过孔不但产生对地的寄生电容,同时也存在着寄生电感,其电气特性的等效模型如图2所示。

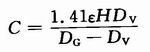

过孔的寄生电容给电路造成的影响主要是使数字信号上升沿减慢或变差,降低了电路的速度。过孔的寄生电容值越小,影响越小。若过孔在铺底层上的隔离孔直径为DG,过孔焊盘的直径为Dv,PCB厚度为H,板基材料介电常数为ε,则过孔寄生电容C的大小近似于:

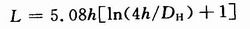

过孔寄生电感的主要影响是降低了电源旁路电容的有效性,使整个电源供电滤波效果变差。若L为过孔的寄生电感,h是过孔的长度,DH是中心钻孔的直径,则可以用下面的公式来简单计算一个过孔近似的寄生电感:

从上式可以看出,过孔直径对电感的影响较小,过孔长度对电感影响较大。在PCB中,通常旁路电容一端通过一个通孔连接到地平面,另一端也通过一个通孔连接到电源平面,因此通孔电感的影响会增加1倍。

2.3 传输线拐角对传输通道信号完整性问题的贡献

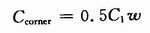

当信号沿均匀连线传播时,不会产生反射和传输信号的失真。但传输线上的拐角会使传输线处的阻抗发生变化,致使信号出现部分反射和失真。根据导线单位长度电容C1(单位:pF/in),导线线宽ω(单位:in),可通过下面公式简单估算每个拐角的寄生电容Ccorner:

在高密度电路板中信号线线宽较窄时,其拐角的寄生电容量引起的时延累加一般不太可能对信号完整性有很大影响。但对于高频敏感电路,如高频时钟线路,应考虑拐角寄生电容所产生的累加效应。

3 利用布线技巧抑制信号完整性问题

当信号从驱动源输出时,构成信号的电流和电压将互连线看作一个阻抗网络。当信号沿阻抗网络传播时,它不断感受到互连线所引起的瞬态阻抗变化。如果信号感受到的阻抗保持不变,则信号不失真。一旦阻抗发生变化,信号就会在变化处产生反射,并在通过互连线的剩余部分时发生失真。如果阻抗改变程度足够大,失真就会导致错误的触发。在信号完整性优化设计过程中,一个重要的设计目标就是:将所有的互连线都设计成均匀传输线,并减少所有非均匀传输线的长度,让整个网络中的信号所感受到的阻抗保持不变。基于此,可以归结出一些利用布线技巧抑制信号完整性问题的方法:印制导线的走线形状不要缠结、分支或硬拐角,尽量避免T形线和桩线;尽量保持同一网络信号线的线宽,减少线宽变化;减少传输线长度,增大导线宽度;要尽量增大导线间的距离;尽量减少高速信号线的过孔及拐角,减少信号线的层间转换;合理选择过孔的尺寸大小;减小信号环路面积及环路电流。总之,任何改变横截面或网络几何形状的特征都会改变信号所感受到的阻抗。布线中减少信号完整性问题的重点就是减少传输线上的阻抗突变,让整个网络中的信号所感受到的阻抗保持不变。

4 结语

随着嵌入式系统的发展,信号完整性成为嵌入式系统PCB设计中的一项极其重要的内容,影响着整个PCB设计的成败。在电路确定、元器件选定、PCB布局确定的情况下,可通过布线技巧来抑制信号完整性问题的出现,提高PCB的可靠性,将信号完整性问题引发的损失降到最低。

- 日本PCB产量连续7个月下滑(06-02)

- 台面板厂产能大幅调降波及PCB业(06-27)

- PCB旺季不旺,产值较第三季下滑4%(12-19)

- 2012年全球PCB行业发展概况(04-19)

- IPC发布2012年4月份PCB行业调研报告(05-30)

- IPC发布2012年5月份PCB行业调研报告(07-04)