从体系结构的演变看高性能微处理器的发展趋势

了系统的功耗。例如,在华威处理器中设计了若干32位可重构乘法器,每个可重构乘法器可以完成32位乘法、若干个16位乘法或者8位乘法。因此,华威处理器可以采用一条指令完成16个8位数据的乘(累)加操作;一条指令可以完成8个16位数据的乘(累)加操作;一条指令可以完成4个32位数据的乘加操作;一条指令可以完成4个32位数据的累加操作;一条指令可以完成16个索引、16个地址计算和16次数据加载操作;两条指令完成16个8位数据累加操作;两条指令可以完成8个16位数据累加操作;两条指令可以完成对256项、8位元素的数据表进行的16路并行查找。

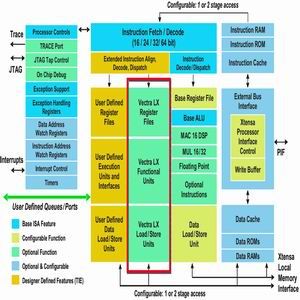

Tensilica的可配置技术是可重构处理器的重要代表。例如,Vectra LX定点向量DSP引擎就是通过配置选项在Xtensa LX可配置处理器的基础上建立起来的。即Vectra LX定点DSP引擎是Xtensa LX微处理器内核的一种配置。该定点DSP引擎是一个3发射SIMD处理器,具有四个乘法器/累加器(四MAC),它可以处理128位的向量。128位向量可以分成8个16位或者4个32位的元素。整个Vectra LX DSP引擎是用TIE (Tensilica's Instruction Extension)语言开发的,通过修改可以适合不同的应用领域。Vectra LX DSP引擎增加了16个向量寄存器(每个寄存器160位宽)、四个128位的向量队列寄存器、第二个load/store单元和210多条现有Xtensa LX处理器指令集体系结构中的通用DSP指令。Vectra LX DSP引擎如图4所示。

图4 Vectra LX DSP体系结构框图

结 语

作为信息产业的核心技术,微处理器体系结构正在发生很大的变化,而这种变化无不体现出市场需求的强大动力。现代微处理器,无论是通用微处理器还是数字信号处理器在体系结构方面正在趋于融合。通用处理器通过增加媒体处理指令来提高数据处理器能力;而数字信号处理器也借鉴了通用处理器的体系结构,使得数字信号处理器的数据处理器能力更加强大、管理更加灵活。同时,随着嵌入式应用的需求,对功耗的要求也越来越苛刻,使得可重构处理器在未来将会起到重要的作用。由于不同的应用需求可以通过重构技术获得所需要的微处理器系统架构,这将大大提高产品的竞争力,同时也降低了整个系统的功耗和成本。

- 多核体系结构的发展(03-06)

- 阵列处理器系统芯片的发展(06-12)

- 嵌入式数控系统软硬件体系结构(09-19)

- 嵌入式处理芯片设计的新动向和新设计方式(02-04)

- Maxim推出用于超声检测的汽车应用SoC(09-10)

- K-micro推出MIPS子系统 进军无源光网络市场(02-15)