从体系结构的演变看高性能微处理器的发展趋势

和时钟频率的乘积成正比。时钟速率同系统结构的关键路径时延有关,而IPC和如下因素有关:程序中潜在的指令级并行性、体系结构字长宽度、指令窗口大小和并行性开发策略。超标量处理器一般通过增加发射逻辑提高IPC,这将导致更宽的发射窗口和更复杂的发射策略。

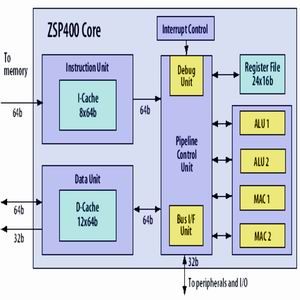

众所周知,超标量处理器是通用微处理器的主流体系结构,几乎所有商用通用微处理器都采用超标量体系结构。而在DSP方面,LSI 逻辑公司的 ZSP200、 ZSP400、ZSP500和ZSP600均采用超标量体系结构。ZSP200采用并行MAC和ALU运算部件,2发射超标量结构;ZSP400采用双 MAC单元、4 发射超标量处理器体系结构;ZSP500为4发射体系结构、采用增强型双MAC和双ALU运算单元;ZSP600采用4MAC和双ALU运算部件,每个时钟周期发射6条指令。图1为ZSP400结构框图。

图1 ZSP400 内核超标量体系结构框图

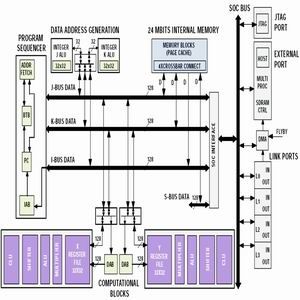

ADI公司的TigerSHARC系列采用静态超标量体系结构。该系列采用了许多传统超标量处理器的特征,如load/store结构、分之预测和互锁寄存器堆等技术。每个时钟周期发射4条指令。而静态超标量的含义是指指令级并行性识别是在运行之前,即编写程序时确定的(事实上以VLIW结构为基础)。同时,Tiger SHARC系统处理器采用SIMD技术,用户可以对数据进行广播和合并。所有寄存器均是互锁的,支持简单的编程模型,该模型不依赖于不同型号间的时延变化。分支目标缓冲器BTB为128位,可以有效减小循环操作和其它非顺序代码的执行时间。图2为TigerSHARC系列中的ADSP-TS201S结构框图。

图2 ADSP-TS201S静态超标量体系结构框图

超长指令字VLIW体系结构

自从耶鲁大学的J.A Fisher于1979年首次提出VLIW体系结构以来,先后由耶鲁大学开发出基于跟踪调度(Trace Scheduling)技术的MultiFlow处理器和Cydrome公司Bob Rau等人开发的基于巨块调度(Superblock Scheduling)的Cydra-5处理器。但直到九十年代中期,基于VLIW结构的处理器基本上停留在实验室原型机阶段。因为VLIW本身固有的几个关键问题一直没有彻底解决,导致了其后的商用处理器体系结构从RISC转向了超标量和超流水,而不是VLIW。尽管如此,由于VLIW结构的许多优点仍然使许多研究机构竞相对该技术进行坚持不懈地研究,并在体系结构和编译器方面实现了突破,其中最重要的是解决了目标代码兼容问题并支持推断推测机制(尽管大部分处理器仅支持部分推断推测机制)。这之后出现了Philip的Trimedia、Equator的MAP1000A媒体处理器、Chromatic的Mact、TI的TMS320C6XX、Transmeta的Crusoe以及INTEL和HP联盟提出的IA-64体系结构(EPIC)。事实上VLIW作为下一代高性能处理器体系结构的首选技术已成共识,该体系结构和优化编译器形成的SIMD指令流将更加适合多媒体数据处理。

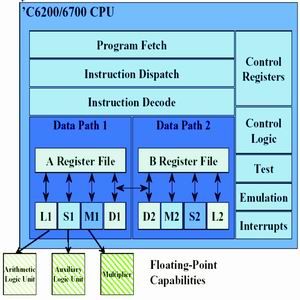

TI的TMS320C6系列是典型的超长指令字VLIW体系结构,该系列每个指令周期可以执行8条32位指令,C62为定点处理器,C67为浮点处理器。C62和C67系列的CPU内核是相同的,包含32个通用寄存器、8个执行部件。C64包含64个通用寄存器和8个执行部件。8个执行部件包含2个乘法器和6个ALU。支持8/16/32数据类型,所有指令均为条件执行,减小了分支指令开销。图3为C62和C67系统框图。

图3 基于VLIW体系结构的TMS320C6系统框图

中国科学院声学研究所在"973国家重大基础研究发展规划"资助下研制成功国内第一款基于多发射VLIW和SIMD技术的具有可重组结构的高性能微处理器芯片-华威处理器(SuperV)。该处理器为四发射VLIW处理器,当执行向量处理功能时,每个周期可执行35个操作。在执行32位乘累加操作时可获得2.9 GOPS 的数据处理速度;执行16位乘累加操作时可获得5.1 GOPS 的数据处理速度;执行8位乘累加操作时可获得9.3 GOPS 的数据处理速度。该处理器是目前国内数据处理能力最强的微处理器,可以广泛应用于信息家电、网络通信、声音图像以及雷达声纳等信号处理领域。

可重构处理器架构

从二十世纪七十年代开始的第一代CISC处理器开始至今,微处理器体系结构已经经过了三代。然而,即使是第三代的RISC技术仍然停留在固定模式的体系架构设计。随着ASIC和SOC技术的发展,微处理器设计进入到第四代,即后RISC和可重构处理器时代。其重要特征是系统架构不再采用固定模式,而是将DSP的灵活性与硬线连接的专用性相结合,使得微处理器可以针对不同的应用需求建立自己独特的体系结构,达到性能最优、功耗更低的目的。

华威处理器(SuperV)体系结构不仅基于RISC、VLIW和SIMD技术,而且采用了可重构技术,使得用户在不增加硬件开销的情况下通过对系统功能部件的重构完成对不同应用的处理,不仅提高了系统性能,而且大大降低

- 多核体系结构的发展(03-06)

- 阵列处理器系统芯片的发展(06-12)

- 嵌入式数控系统软硬件体系结构(09-19)

- 嵌入式处理芯片设计的新动向和新设计方式(02-04)

- Maxim推出用于超声检测的汽车应用SoC(09-10)

- K-micro推出MIPS子系统 进军无源光网络市场(02-15)