锂离子电池管理芯片的研究及其低功耗设计-----版图实现及验证

5.1版图设计

5.1.1数模混合信号电路版图设计

版图设计是集成电路的物理实现,是电子系统和工艺间的桥梁。总的说来,版图设计以减少芯片面积、提高电路性能、节省设计费用为目标。对于电源管理芯片而言,由于对电路性能要求比较高,采用自上而下的分层设计方法,能够更有效地实现缩小芯片面积,降低制造成本。

自上而下是指从电路图或逻辑图设计版图。首先,要对电路或逻辑进行分析,主要分析对系统性能、版图面积或芯片布局起很重要作用的关键部分。然后,开始布局设计,解决电路或逻辑图中的每个功能单元在版图中位置的摆放、压点分布、电源线、地线以及主要信号线的走向等。完成分层布局后,接下来则采取自下而上的方法,从元器件级到子单元,再由子单元到单元,直至完成整个芯片设计。需要指出的是,在电路或逻辑设计之初,不一定对版图结构进行深入考虑,甚至有些是不可预料的。因此,版图设计是暴露出的问题,要求电路设计还要进行重新修改或对电路参数进行调整,而且往往这需要多次反馈才能满足要求。

在混合信号电路版图设计中,除可以采用一些常见的设计方法来实现性能、面积的双赢外,还有一些重要的因素必须认真考虑,比如噪声。影响噪声的主要因素有:开关引起的电源噪声、通过衬底引起的耦合、芯片连线层次的内连线耦合及包括了封装寄生效应在内的I/O耦合。几乎所有模拟电路都会由于数字电路噪声而恶化,现有的技术可以尽量减小噪声的影响,但是无法完全消除噪声[116]。

在混合信号电路中,由于电源线的电阻和电感,当逻辑模块的开关电流将引起电源电压的扰动,所以在设计中必须加以重视。如果模拟电路和逻辑电路的电源线是共用的,则必然要受到电源扰动的影响。在电路设计层次,正如前一章提出的,降低电源电压噪声的影响本质上是降低电路与电源电压的相关性,这可以设计高PSRR的电路实现;在版图设计层次,则可以将模拟和逻辑电源线分开,减小电源扰动影响,但是这种方法显然将给版图设计电源线分布和设计验证阶段增加了额外的难度。而降低电源总线上的串联电阻和电感能有效地降低电源噪声,这需要在芯片级布局将电源线均匀分布或是使电源线宽度或沿线通孔最大。

而且,有必要对模拟电路电源总线仔细设计,以使逻辑干扰效应降到最小。

5.1.2系统版图

系统版图设计中,除要注意上述所提出的混合电路版图设计中的共性问题以外,还要对系统中的一些特殊器件版图作专门考虑,如PNP管的实现、高压管的版图设计等。

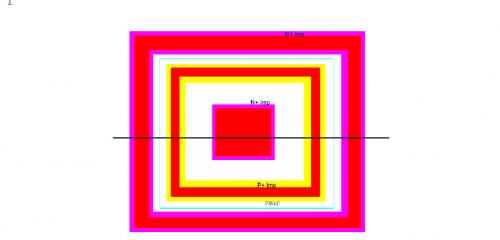

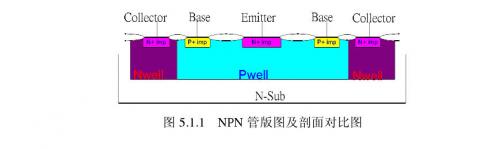

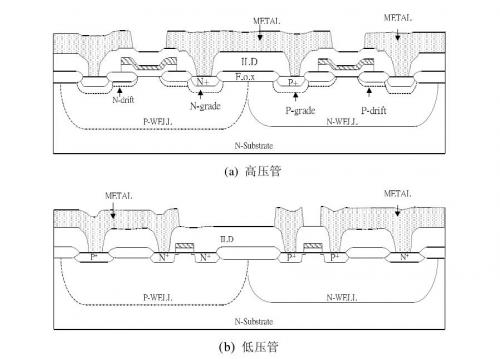

图5.1.1给出了纵向衬底NPN管的剖面图及版图结构。当基极和集电极同时接电源电压VDD端时,则从发射极可以输出一个相对于V DD的V BE。图5.1.2所示的则是系统所用高压、低压管的剖面图。低压管的工作电压在0V~5V,高压管的工作电压可以在0V~30V间变化。

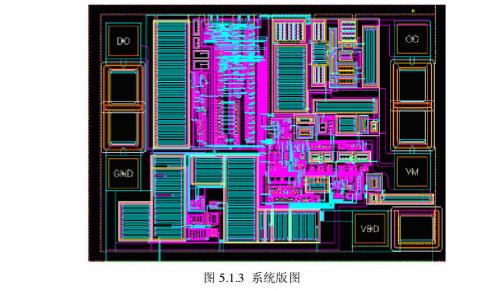

图5.1.3给出了系统版图。芯片占用面积为0.77mm 2。图中可见,电阻所占面积较大。原因在于,为了降低电路静态功耗,取样电路和电压基准源中采用的电阻面积较大,而且为了达到高精度电压检测,必须采用Trimming工艺调整电阻阻值,这又进一步增大了电阻所占用的版图面积。

5.2系统后模拟验证

5.2.1版图验证

版图验证是版图设计中一个必不可少的重要环节。版图验证通常有两种方法,一种是DRC,ERC和LVS验证;另一种是DRC,ERC和晶体管级网表提取与开关级模拟验证。

其中,DRC和ERC是对版图进行几何设计规则和电学规则检查,关键在于编写合格的检查文件,按设计规则,逐条编写。LVS检查又称网表一致性检查,即对版图进行器件及其连接关系进行提取,获得电路网表,并和原设计的电路图或逻辑图进行比较,检查其一致性。不言而喻,LVS检查存在一定局限性,对于速度不高、无竞争、分布寄生参数影响不大的电路,有一定的效果,反之,则需要后模拟验证。

后模拟(Post-Simulation)的验证策略是包括从版图上提取分布寄生参数在内的仿真验证。但对于元器件较多的电路,要进行晶体管级的仿真验证,现有的软硬件都有些力不从心。因此,后模拟验证方式不能一概而论,需要根据电路性质、电路规模和设计模式选用不同的验证方式。数字电路可以根据规模大小、功能复杂程度采用开关级或分级逻辑仿真,所用软件主要采用时钟驱动算法分析电路结点的逻辑状态;模拟电路则一般采用SPICE验证,利用求解非线性微分方程组的数值计算方法求解电路方程。由此可知,因为计算方法和输出结果类型的巨大差异,逻辑仿真和电路仿真不可能完全统一,所以混合信号的仿真问题,在没有一个统一的进行数模混合仿真算法的前提下,只能取得模拟精度和速度的折衷。

本文所设计的系统包括了模拟电路和逻辑电路部分,采用的后模拟验证途径为,从版图中提取晶体管及其连线的R、C参数,在此基础上进行HSPICE电路仿真。为了解决前面所提到的混合信号模拟问题,在模拟时采用了以下的处理方法,即按照电路仿真方法对整个电路进行性能模拟,但在模拟中做一些必要的假定。另外,采用POWERMILL软件,在降低仿真精度的基础上,利用查表方式,快速地对系统进行功能和功耗模拟验证。